CPLD説明:プログラム可能なロジックデバイスのガイド

電子設計の動的な世界では、複雑なプログラム可能なロジックデバイス(CPLD)が汎用性の高いツール、適応性、精度、効率をシームレスにブレンドするものとして際立っています。これらのデバイスは、プログラム可能なマクロセルと支配的な相互接続マトリックスを導入することにより、回路設計に革命を起こし、顕著な信頼性を備えた複雑なロジック関数の作成を可能にしました。1980年代の創業から、ネットワーキング、自動車、航空宇宙などの近代的な産業における重要な役割まで、CPLDは柔軟性とパフォーマンスの両方を求めるために必要なことが証明されています。この記事では、CPLDSの旅、独特の機能、実用的なアプリケーション、およびデジタルロジックデザインの基礎となるプログラミング方法論を掘り下げています。カタログ

CPLDの概要

複雑なプログラム可能なロジックデバイス(CPLD)の支配の中で、支配的な相互接続マトリックスを通じて織り込まれたプログラム可能なロジックマクロセルの洗練されたタペストリーを発見します。これらのマクロセル(MC)および入出力(I/O)ユニットラインを使用すると、ユニークな機能の構造を構成して、回路を巧みに設計することができます。複雑な相互接続タイミングに困惑しているデバイスとは異なり、CPLDは不動の金属ワイヤを利用します。この特徴は、彼らに一貫した予測可能な時計の動作を与え、タイミングの予測をより信頼性が高く正確にします。

旅と利用

1970年代は、プログラム可能なロジックデバイス(PLD)の出現を告げ、プログラム可能なマクロユニットへの動きを促進しました。このシフトにより、十分な設計の柔軟性が導入され、静的デジタルサーキットとは一線を画していますが、当初はより単純な回路に制約されていました。1980年代半ばのCPLDSの出現は、この景観に革命をもたらし、複雑な回路設計への道を開いた。それ以来、彼らはネットワーキング、自動車電子機器、CNC加工、航空宇宙システムなどの産業の構造に織り込まれています。かつて細心の手動労働を要求していたCPLDSが単純化されたプロセスをどのように単純化し、効率が顕著に飛躍するかを思い出すことができます。

CPLDの特徴

CPLDは、適応性のあるプログラミング、広範な統合、Swift開発機能、幅広い適用性と経済的生産コストを通じて、自分自身を区別します。彼らは、最小限のハードウェアエクスペリエンスを持つ人々にアピールし、徹底的なテストを必要としない信頼できる安全な製品として機能します。大規模なサーキットデザインにおける彼らの腕前の証として、CPLDはプロトタイプ開発で重要な役割を果たし、10,000ユニット未満のランニングを提供し、あなたにとって有用な能力を具体化します。CPLDSが進化するプロジェクトの要求に合わせて調整する熟練度は、しばしば彼らに感謝を獲得し、動的環境での実際の汎用性を強調します。

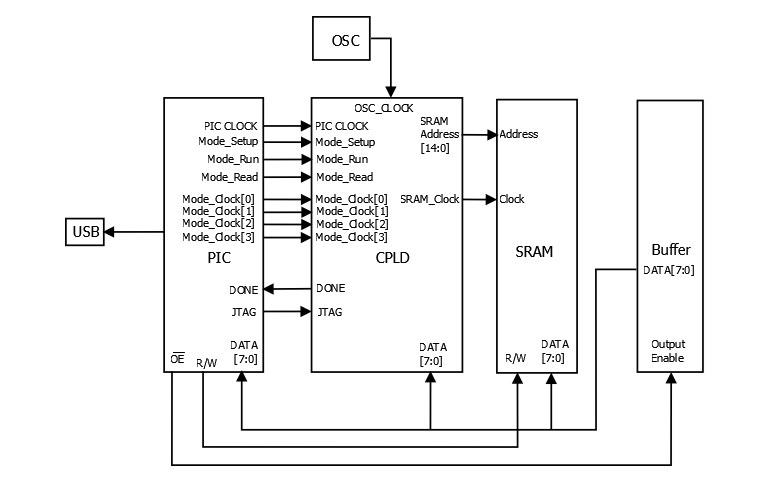

アプリケーション方法

これらの統合サーキットを使用すると、開発プラットフォーム上の回路図とハードウェアの説明言語の両方を使用して、ニーズに合わせたロジック関数を詳しく説明できます。たとえば、留守番電話の設計では、コンピューターで準備され、ハードウェアの説明が準備され、コンパイルされています。ダウンロードケーブルを利用して、コードはテスト、トラブルシューティング、および設計の強化を含むシステム内プログラミングのためにCPLDに転送されます。成功したデザインは、CPLDチップを複製することにより、大量生産されます。信号システムのようなプロジェクトでは、設計プロセスを繰り返すことが必要になり、家を再構築して新しさを回復します。この繰り返しの方法論は、多くの場合、スキルと自信の両方を高めるための基礎を築きます。

主要なバリエーション

長年にわたり、Altera、Lattice、Xilinxなどの企業は、CPLDの顕著な系統を発表してきました。注目に値する例には、アルテラが含まれます EPM7128S、格子 LC4128V、xilinx's XC95108 。これらのモデルは、多様なグローバルアプリケーション全体で顕著な役割を見つけました。これらの異なる製品と協力する特権を持っている人は、特定の機能を最適化する微妙で強力な違いについて頻繁に発言します。これは、各バリアントが独自の魅力を保持している特定のプロジェクトの需要の影響を受ける素晴らしい選択プロセスを反映しています。

FPGAおよびCPLDの識別と分類

|

側面 |

CPLD |

FPGA |

|

論理的な動作形成 |

製品用語構造を使用して論理的な動作を形成します。

例:Lattice ISPLSIシリーズ、Xilinx XC9500シリーズ、Altera Max7000S

シリーズ、格子マッハシリーズ |

テーブルルックアップ方法を使用して論理的な動作を形成します。

例:Xilinx Spartanシリーズ、Altera Flex10k、ACEX1Kシリーズ |

|

適合性 |

アルゴリズムと組み合わせロジックに適している、機能します

限られたトリガーと豊富な製品用語でより良い |

シーケンシャルロジックに適しているため、より適切に機能します

トリガーが豊富な構造 |

|

タイミング遅延 |

連続配線構造は均一になります

予測可能なタイミングの遅延 |

セグメント化された配線構造は、予測不可能なタイミングにつながります

遅延 |

|

プログラミングの柔軟性 |

固定内部回路はプログラミング用に変更されています。

ロジックブロックレベルのプログラミングが使用されます |

内部配線はプログラミング用に変更されます。論理

ゲートレベルのプログラミングにより、柔軟性が向上します |

|

統合 |

FPGAと比較して統合が低くなります |

より複雑な配線構造とのより高い統合と

ロジック実装 |

|

使いやすさ |

E2PROMまたはFastFlashを介したプログラミングで使いやすい。

外部メモリチップは必要ありません |

プログラミングを保存するには外部メモリが必要です

より複雑な使用につながる情報 |

|

速度と予測可能性 |

より速い速度とより良いタイミングの予測可能性

ロジックブロック間のまとめの相互接続 |

速度が遅く、予測可能なタイミングが低下します

ゲートレベルのプログラミングと分散間接続 |

|

プログラミングテクノロジー |

E2PROMまたはフラッシュメモリプログラミングを使用します。プログラミングデータ

システムの電源が切れたときに保持されます。のプログラミングをサポートします

プログラマーまたはシステム |

SRAMプログラミングに基づいています。プログラミングデータはいつでも失われます

システムは電源が切れており、リロードする必要があります。ダイナミックをサポートします

構成 |

|

機密性 |

より良い機密性を提供します |

より低い機密性を提供します |

|

消費電力 |

一般的に、特により高い消費電力

より高い統合 |

CPLDと比較して消費電力が低くなっています |

CPLDのプログラミング言語

複雑なプログラム可能なロジックデバイス(CPLD)がどのようにプログラムされているかを分析することは、多用途のハードウェアソリューションを作成する礎石です。CPLDをプログラミングするための歴史的な方法は、はしご図またはハードウェアの説明言語(HDL)に依存しており、Verilog HDLとVHDLは主要な選択です。選択した言語は、設計戦略と実装の運用効率の両方を形作ることができます。

• Verilog HDL:Verilog HDLは、デジタルロジック設計で使用される方法論を反映した、単純な構文と堅牢なシミュレーション機能のために大切にされています。Electronic Design Automation(EDA)ツールとの統合により、合成とシミュレーションをシームレスに実施できます。VerilogのC様構文は、プログラミングのバックグラウンドを持つ人々の侵入に対する障壁を下げることが観察されており、幅広い産業部門のデザインから展開への旅を早めています。

• VHDL:VHDLは、HDLプログラミングに、より精巧で表現力のあるオプションを提供します。多くの場合、航空宇宙および防衛産業で評価されている特性である綿密な文書と厳密なタイプチェックを要求するプロジェクトの選択です。小規模プロジェクトにおけるVHDLの潜在的な複雑さにもかかわらず、その規律ある構造は、安全性が支配的な環境では非常に信頼できるデザインの作成をサポートしていることに注意してください。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

NMOSトランジスタ:設計、操作、アプリケーション

12/29/2024で公開されています

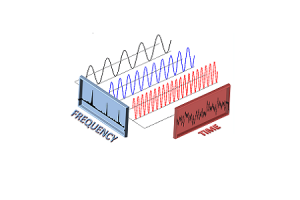

高速フーリエ変換(FFT):デジタル信号処理の革新

12/29/2024で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/18/8000で公開されています 147780

-

USB-Cピンアウトと機能

04/18/2000で公開されています 112047

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/18/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/18/0400で公開されています 83806

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79607

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66986

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63113

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63048

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54097

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52199