CPUメモリセグメンテーションのコードセグメント(CS)レジスタ:完全なガイド

CPUは、メモリに保存されている命令にアクセスしてプログラムを実行し、このプロセスの重要な部分はコードセグメント(CS)レジスタです。CSレジスタは、特にX86アーキテクチャなどの古いシステムでセグメント化されたメモリモデルを使用するCPUで必要です。この記事では、CSレジスタが命令ポインター(IP)でどのように機能してメモリを管理し、メモリセグメンテーションを理解することが今日依然として重要である理由について説明します。カタログ

コードセグメント(CS)レジスタとは何ですか?

コードセグメント(CS)は、メモリ内のコードセグメントの開始アドレス(またはベースアドレス)を保持するCPUの専門的なレジスタです。コードセグメントは、プログラムの実行可能コードを含む専用のメモリ領域です。したがって、CSレジスタは、プログラムの指示が保存されているメモリ内の場所を指し、CPUがそれらの命令を取得および実行できるようにします。CSレジスタの役割は、別の重要なレジスタである命令ポインター(IP)との関係を考慮すると、より明確になります。CSレジスタはコードセグメントの開始アドレスを保持しますが、IPレジスタは、そのセグメント内で実行される次の命令のオフセットアドレスを追跡します。CSとIPレジスタは、CPUがメモリ内の次の命令の正確な位置を特定できるようにする論理アドレスを形成します。例えば:

CS =コードセグメントのベースアドレス

IP =次の命令のオフセットアドレス

組み合わせると、CPUは物理アドレスを計算します CS:IP 次の命令を見つけて実行します。

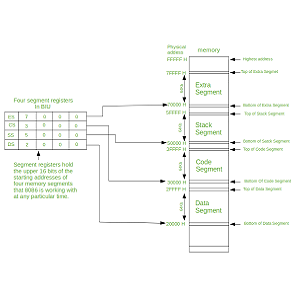

セグメント化されたメモリモデル

CSレジスタが存在する理由を理解するには、X86プロセッサなどの古いアーキテクチャで一般的に使用されていたセグメント化されたメモリモデルを理解する必要があります。このモデルでは、メモリはセグメントに分割され、それぞれが異なる目的を果たします。

•コードセグメント(CS):実行可能コードを保存します。

•データセグメント(DS):プログラムで使用される変数とデータを保存します。

•スタックセグメント(SS):関数呼び出し、ローカル変数、および制御フローを管理します。

•追加セグメント(ES):追加のデータストレージに使用されます。

セグメント化されたメモリモデルは、メモリ管理に構造化されたアプローチを提供するように設計されており、コード、データ、およびスタックのためにメモリを異なる領域に分割しやすくなります。このアプローチにより、CPUはメモリをより効率的に管理し、異なるタイプのデータを別々のセグメントに保持することにより、より良いメモリ保護を提供することができました。初期のコンピューティングシステムでは、CPUは一度に限られた量のメモリにのみアクセスできました。セグメント化されたメモリモデルにより、プログラマーは、より小さく、より管理しやすいセクションに分割することにより、より多くのメモリを使用することができました。また、セグメントレジスタはベースアドレスを保持できるため、この設計はアドレスのサイズを縮小するのにも役立ちますが、オフセット(IPなど)はベースに追加される値が小さくなります。最新のプロセッサは、すべてのメモリが単一の連続空間として扱われるフラットメモリモデルを使用することがよくありますが、セグメンテーションの原理は現在でもCPU設計に影響を与えています。実際、一部の最新のシステムは、メモリ保護や仮想化などの特定の目的でセグメンテーションを使用し続けています。

CSとIPレジスタの関係

コンピューターの中央処理ユニット(CPU)では、CS(コードセグメント)レジスタとIP(命令ポインター)レジスタの関係は、指示を取得して実行するプロセスにとって重要です。一緒に、これらの2つのレジスタは、メモリ内の次の命令の位置を決定し、CPUがプログラムのフローの各ステップで何を実行するかを正確に知っていることを確認します。

CSレジスタは、実行可能コードが存在するメモリに特定のセグメントの開始アドレスを保持します。このセグメントベースのアドレス指定は、セグメント化されたメモリアーキテクチャで必要であり、CPUはコード、スタック、データセグメントなどのさまざまなタイプのデータの論理セクションにメモリを分割できるようにします。一方、IPレジスタは、現在のコードセグメント内で実行する次の命令を追跡するポインターとして機能します。IPレジスタにはオフセット値が含まれています。これは、次の命令が配置されているコードセグメントの開始点からどれだけ離れているかを示します。

実際には、この関係は次のように機能します。CPUは最初にCSレジスタに保存されているアドレスを読み取り、メモリ内のコードセグメントの開始点を特定します。次に、IPレジスタに保存されている値を使用して、CSレジスタが提供するベースアドレスにIPオフセットを追加することにより、次の命令の正確な場所を計算します。これら2つの値の組み合わせ、CSレジスタのベースアドレスとIPレジスタのオフセットは、次の命令が保存されている物理メモリアドレスを生成します。

物理アドレスが計算されると、CPUはメモリから命令を取得し、それを解読し、実行します。実行後、IPレジスタは更新され、次の命令を順番に指し示し、プロセスが繰り返されます。命令を取得、デコード、および実行するこの連続サイクルは、CPUがプログラムを実行するコアメカニズムです。CSとIPレジスタは、CPUが次の命令を実行するためにメモリ内を正確に検索する場所を正確に把握していることを確認します。この関係は、特にセグメント化されたメモリアーキテクチャを備えたシステムで、プログラムの正しい実行フローを維持するのに適しています。

CSレジスタがプログラミングで重要なのはなぜですか?

CSレジスタは、特にセグメント化されたメモリモデルに依存する環境では、低レベルのプログラミングとシステム開発において優れています。実行可能な指示が保存されているコードセグメントの境界を定義し、プログラムが割り当てられたメモリスペース内で実行されるようにします。エラーを回避し、システムの安定性を維持するには、これらのセグメントの境界を適切に管理する必要があります。セグメント管理の不十分な問題の1つは、アクセス違反です。これらは、プログラムが指定されたコードセグメントの外側のメモリをタクセスしようとすると発生し、クラッシュまたは予期しない動作につながります。たとえば、プログラムがコードセグメントのサイズを超えた場合、隣接するメモリを上書きして、データが破損しているか、不安定なパフォーマンスが発生する可能性があります。

別のリスクは、CSレジスタの不適切な使用による予測不可能なプログラム動作です。CPUが意図しないメモリの領域から指示を実行すると、システムは予測不可能に動作するか、完全にクラッシュする場合があります。これは、プログラマーがCS、DS(データセグメント)、SS(スタックセグメント)などのレジスタを慎重に管理する必要がある初期X86アーキテクチャなど、セグメント化されたメモリを使用した古いシステムで頻繁に問題でした。最新のシステムはフラットメモリモデルを使用することがよくありますが、CSレジスタを理解することは、組み込みシステム、オペレーティングシステム設計、または直接メモリコントロールを必要とする他のフィールドで作業するために重要です。これらの分野では、メモリ境界の効果的な管理により、システムの信頼性が保証され、データの腐敗が防止され、診断が難しいバグが回避されます。低レベルのプログラマーの場合、CSレジスタをマスターすることは、安定した効率的なソフトウェアの構築の重要な部分です。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

BitStreams and BitTorrent:分散型ファイル共有、テクノロジー、および法的意味合いの調査

01/6/2025で公開されています

組み込みシステムの中割り込みサービスルーチン(ISR):概念、重要性、および設計

01/6/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/19/8000で公開されています 147783

-

USB-Cピンアウトと機能

04/19/2000で公開されています 112073

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/19/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/19/0400で公開されています 83831

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79646

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 67013

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63136

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63067

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54099

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52229