デジタルフェーズロックループ(DPLL):設計、コンポーネント、および操作

このガイドでは、その精度と信頼性で知られる最新のデジタルサーキットの重要な部分であるデジタルフェーズロックループ(DPLL)を探ります。DPLLは、さまざまな業界での変調、復調、同期などのタスクで役割を果たしています。コンポーネントとその仕組みを分解することにより、この記事では、従来のアナログシステムに対するDPLLの設計、機能、および利点を強調しています。カタログ

機器の探索

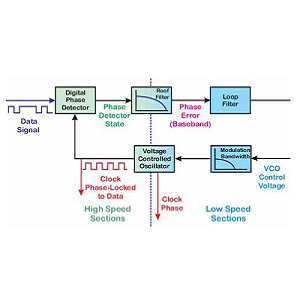

デジタルフェーズロックループ(DPLL)は、デジタル回路技術のブレークスルーによって駆動される、現代のテクノロジーの典型的な要素として立っています。その汎用性の高いアプリケーションには、変調、復調、周波数合成、FMステレオデコード、色のサブキャリアの同期、画像処理が含まれます。これらのデバイスは、信頼性、コンパクト、コスト効率のために輝き、DCドリフト、デバイスの飽和、電力と温度の変動に対する感受性など、アナログ位相ロックループの固有の欠点を効果的に克服します。個別のサンプルを管理する能力は、広範な採用に効率的に貢献します。ユニークなことに、位相ロックループは位相フィードバック制御システムとして動作します。DPLLは、連続アナログ電圧ではなくエラーを管理するための離散デジタル信号を利用することにより上位を証明し、全デジタル位相ロックループ(DPLL)として説明につながります。

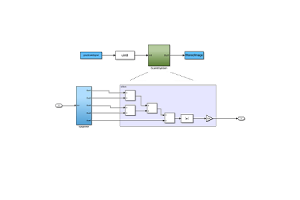

DPLLは、位相参照抽出回路、クリスタルオシレーター、周波数仕切り、位相コンパレータ、およびパルス補償ゲート:コンポーネントで構成されています。フェーズコンパレータが基準信号を注意深く精査するため、周波数分割器の出力は目的の周波数と整合します。より高い局所周波数が観察されると、周波数を減らすためにパルスが戦略的に除去されますが、周波数が不十分な場合、パルスが追加されて同期を改善します。強力なDPLLは、デジタルフェーズ検出器(DPD)、デジタルループフィルター(DLF)、およびデジタル電圧制御オシレーター(DCO)で構成されています。長年の実験とアプリケーションにより、エンジニアはさまざまな産業分野でのDPLLの広大な能力を明らかにし、その運用と改良に関する深い洞察を提供しています。

デジタル位相検出器(DPD)

DPLLの重要なコンポーネントは、入力信号の位相を電圧制御オシレータからの出力と比較するためのサンプリングフェーズ検出器とも呼ばれるデジタル位相検出器です。結果の出力電圧は、位相差を反映して、ループの調整プロセスをガイドします。デジタルフェーズ検出器には、ゼロクロス、フリップフロップ、リードラグ、およびナイキストレートサンプリング検出器のさまざまなタイプがあります。

デジタルループフィルター(DLF)

デジタルループフィルターは、ノイズリダクションとループの応答時間の改良に役割を果たします。是正要素としての機能は重要であり、そのアナログの対応物の義務を反映しています。デジタルフィルター構造の意図的な設計と選択は、DPLLがパフォーマンスの目標を達成できるようにする上で重要です。

デジタル電圧制御発振器(DCO)

デジタルクロックと呼ばれることもあるデジタル電圧制御オシレーターは、アナログVCOと同様に機能し、一連のパルスとして出力を生成します。DLFは、調整信号を送信することにより、これらのパルスのタイミングを管理し、以前の変更に関連する後続のサンプリング期間に影響します。この反復フィードバックループは、経験的研究と理論的強化の両方を通じて改良され、無数の現代アプリケーションの基礎を確立しました。

デジタルフェーズロックループ操作

デジタルフェーズロックループは、周波数の綿密な同期を実現するために設計された徹底的なプロセスを受けます。

信号比較のダイナミクス

最初に、入力信号とローカルオシレーターシグナルは、正弦とコサインとして概念化され、デジタルフェーズ検出器内に評価段階に入ります。検出器は、これらの信号間の位相の矛盾を反映する出力電圧を生成します。このフェーズの比較は、楽器を調整する複雑なプロセスに似ており、対称性と精度のために調和のとれたバランスを維持するための調整が必要です。

周波数調整プロセス

その後、デジタルループフィルターは、高周波ノイズの検出器の出力を巧みにクレンジングするために介入します。この磨かれた信号は、DCO(デジタル制御オシレーター)入力電圧を調整し、局所発振器の周波数に微妙に影響します。周波数の不一致に対処すると、システムはローパスフィルターを利用して、DCOがアライメントに引き寄せられるようにします。この適応メカニズムは、永続的な微調整がシームレスな操作を保証する航空管制などの複雑な環境で見られる継続的な警戒を反映しています。

同期の達成とメンテナンス

局所発振器信号が入力周波数と整列すると、位相差が無効になり、位相検出器とループフィルターの両方から一貫したDC出力が生成されます。周波数を安定させると、DCOはループを同期した「ロックされた状態」に導きます。このバランスは、カオスを回避するために継続的な同期を必要とするエネルギーグリッドの安定した機能を連想させる一貫性に対するループの適性を目撃します。この手順の詳細な進行は、変化する条件の中で同期を達成することに熟練した技術システムにおけるデジタルフェーズロックループの役割を強調しています。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

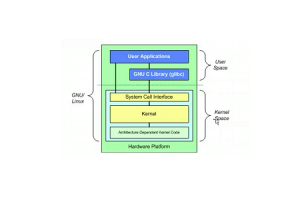

カーネルアーキテクチャの進化と分類

01/7/2025で公開されています

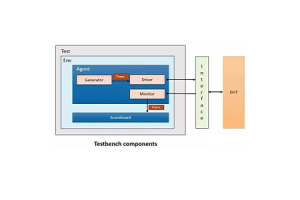

テストベンチへの包括的なガイド:デジタルシステム検証のためのツールとテクニック

01/7/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/18/8000で公開されています 147780

-

USB-Cピンアウトと機能

04/18/2000で公開されています 112042

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/18/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/18/0400で公開されています 83806

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79605

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66986

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63113

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63048

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54097

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52199