EP2S60F672C4 FPGA:機能、アプリケーション、プログラミングおよびデータシートガイド

このガイドでは、IntelのStratix IIファミリーの強力なFPGAであるEP2S60F672C4の明確な概要を取得します。その主な機能、アーキテクチャ、ブロック構造、技術仕様について学び、高度なデジタルデザインにどのように適合するかを理解します。また、プログラミングの手順、アプリケーション、利点、および短所についても説明して、このデバイスをどこでどのように使用できるかを正確に確認できます。カタログ

EP2S60F672C4とは何ですか?

EP2S60F672C4 Intel(以前のAltera)の高密度FPGAであり、Stratix IIファミリーに属しています。90 nm、1.2 V銅SRAMプロセスに基づいて構築され、672ボールFBGAパッケージ内で実質的なロジック容量を提供し、複雑なデジタルシステムに最適です。EP2Sシリーズの一環として、「60」デバイスはStratix IIラインナップのミッドアッパー範囲範囲にあり、ロジック密度、埋め込みメモリ、I/Oリソースのバランスが強いです。堅牢なアーキテクチャと信頼性で知られるこのFPGAは、多くの高度なデザインで信頼できる選択肢のままです。

EP2S60F672C4をお探しですか?現在の在庫、リードタイム、価格を確認するには、お問い合わせください。

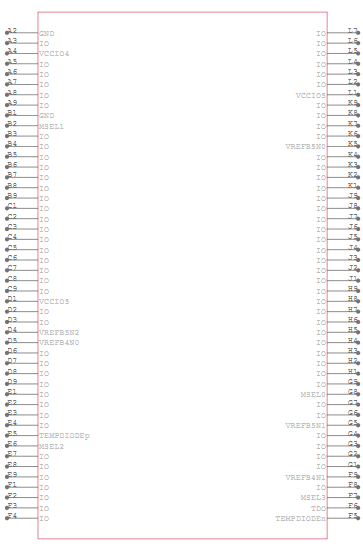

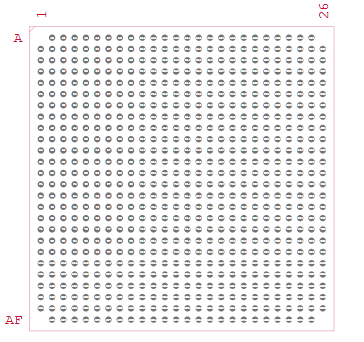

EP2S60F672C4 CADモデル

EP2S60F672C4シンボル

EP2S60F672C4フットプリント

EP2S60F672C4 3Dモデル

EP2S60F672C4機能

• 高度な90 nm、1.2 V CMOSプロセス

EP2S60F672C4は、1.2 Vコア電圧で実行される90 nmの全層銅CMOSプロセスで製造されています。このテクノロジーは、高速化、消費電力の低下、および古いFPGA世代と比較してより大きな論理密度を可能にします。

• 適応ロジックモジュール(ALM)アーキテクチャ

このデバイスは、従来のロジック要素ではなく、ロジックビルディングブロックとしてALMSを使用します。このアーキテクチャにより、リソースの使用率が向上し、同じシリコン領域内でより複雑なロジック関数を効率的に実装できるようになります。

• 高い論理密度

約60,440のロジック要素(24,176の施し)を備えたFPGAは、大規模で洗練されたデジタルデザインをサポートしています。この大容量により、信号処理、通信、組み込み制御システムなどのアプリケーションに適しています。

• Trimatrix™オンチップメモリ

EP2S60F672C4は、3つのタイプのRAMブロック(M512、M4K、およびM-RAM)を統合して、合計約2.4 MBITSの埋め込みメモリを提供します。このミックスにより、小さなFIFO、中型バッファー、および大きなデュアルポートメモリを効率的に実装できます。

• 専用のDSPブロック

このデバイスには、乗算、蓄積、FIRフィルタリングなどの算術演算用に設計された36の専用DSPブロックが含まれています。これらのブロックは、一般的なロジックリソースを節約しながら、計算集約型タスクのパフォーマンスを高めます。

• 高速I/Oおよび信号の完全性

動的位相アライメント(DPA)回路とともに、さまざまなシングルエンドおよび微分I/O標準をサポートします。これらの機能により、最大1 Gbpsの安定した高速データ転送が可能になり、外部コンポーネントとの信頼できる通信が確保されます。

• 豊富な外部メモリインターフェイスサポート

FPGAは、DDR、DDR2、QDR II、RLDRAM II、およびその他のメモリ標準と互換性があります。組み込みインターフェイスサポートは、ボード設計を簡素化し、メモリ集約型アプリケーションの高いデータスループットを実現します。

• 柔軟なクロック管理

最大12個のオンチップPLLにより、クロック乗算、分割、位相シフト、グリッチフリースイッチオーバーが可能になります。クロックドメインを微調整してジッターを減らして、最大500〜550 MHzの内部クロック周波数をサポートできます。

• ビットストリーム暗号化と再構成

EP2S60F672C4は、AESベースのビットストリーム暗号化をサポートして、知的財産を保護します。また、リモート再構成機能も提供し、デバイスを交換せずにフィールド内の更新を可能にします。

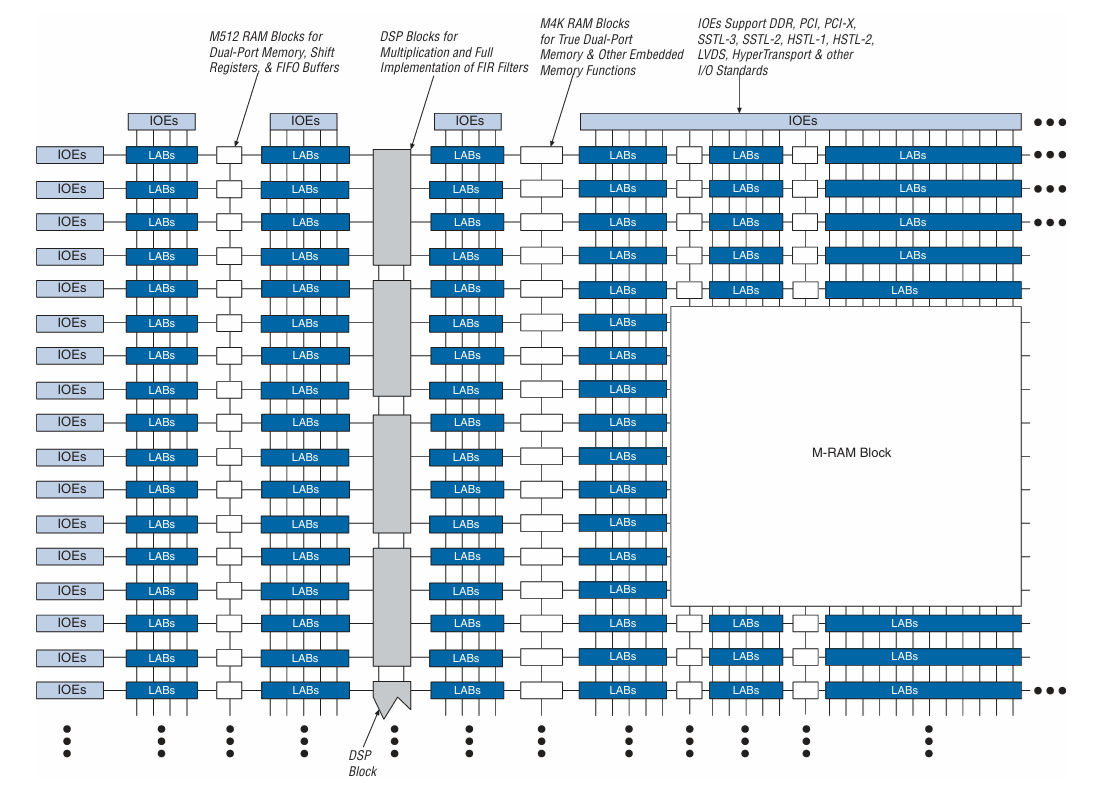

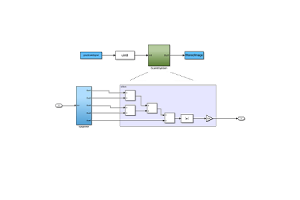

Stratix IIブロック図

EP2S60F672C4に示されているように、Stratix IIブロック図は、FPGAのコアを形成するロジック、メモリ、およびDSPリソースの内部配置を示しています。ロジックアレイブロック(ラボ)は、埋め込みRAMとDSPカラムに囲まれた通常のグリッドに配置されており、高速算術およびオンチップストレージ機能を提供します。周辺I/O要素とクロックネットワークはこの構造を構成し、FPGAと外部デバイス間の効率的なデータ転送とタイミング制御を可能にします。この図は、異なる機能ブロックが物理的に整理されている方法を理解し、配置、ルーティング、およびシステム全体のパフォーマンスを最適化できるため、重要です。

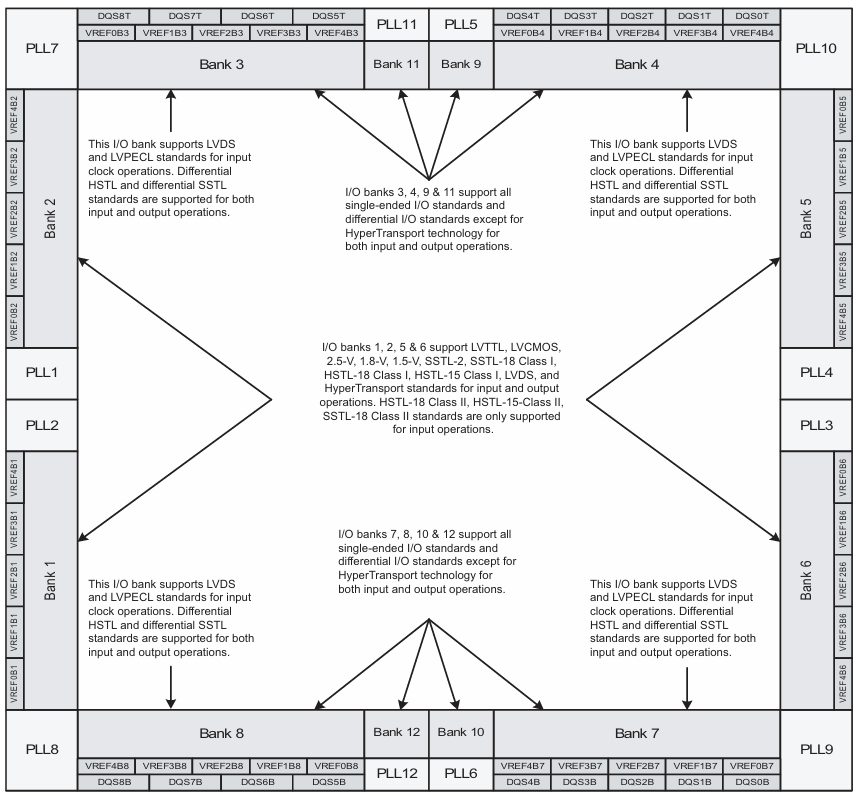

Stratix II I/O Banks図

このStratix II I/O Banks図は、EP2S60F672C4の入出力ピンがどのようにグループ化され、各グループがサポートしているかを示しています。各I/Oバンクは、特定の電圧レベル、シグナリングタイプ、およびLVTTL、SSTL、LVDS、またはクロック入力標準などの機能を処理するように設計されています。このレイアウトは、異なる銀行(例:1、2、5、6対3、4、7、8など)が、エッジでのLVDS/LVPECLクロック入力のサポートを含む、汎用I/Oまたは高速微分シグナル伝達のいずれかに最適化されていることを示しています。適切な銀行の選択により、電気的互換性が保証され、ボードルーティングが簡素化され、高速設計でのFPGAのパフォーマンスが最大化されるため、この構造を理解することはピンを割り当てるときに重要です。

EP2S60F672C4仕様

|

タイプ |

パラメーター |

|

メーカー |

アルテラ/インテル |

|

シリーズ |

Stratix®II |

|

パッケージング |

トレイ |

|

パーツステータス |

廃止 |

|

ラボ/CLBの数 |

3022 |

|

ロジック要素/セルの数 |

60,440 |

|

合計RAMビット |

2,544,192 |

|

I/Oの数 |

492 |

|

電圧 - 供給 |

1.15 V〜1.25 V |

|

取り付けタイプ |

表面マウント |

|

動作温度 |

0°C〜85°C(TJ) |

|

パッケージ /ケース |

672-BBGA |

|

サプライヤーデバイスパッケージ |

672-FBGA(27×27) |

|

基本製品番号 |

EP2S60 |

EP2S60F672C4アプリケーション

1。デジタル信号処理(DSP)およびフィルタリング

EP2S60F672C4は、FIRやIIRフィルター、FFT処理、複雑な算術演算などの高性能DSP関数を実装するのに適しています。専用のDSPブロックは、乗算と蓄積を効率的に処理し、他のタスクの一般的なロジックリソースを解放します。オンチップTrimatrix™メモリは、スムーズなデータバッファリングとパイプラインを可能にします。これは、高いサンプルレートでのリアルタイム処理に最適です。これにより、デバイスは高度なオーディオ、ビデオ、およびレーダー信号アプリケーションに最適です。

2。高速通信とネットワーキング

FPGAの高速I/Oインターフェイスと動的位相アライメント(DPA)回路は、信頼できるギガビットレベルのデータ送信をサポートします。ルーター、スイッチ、バックプレーンの相互接続などのシステムに通信プロトコルと物理層関数を実装できます。大きなロジック容量と柔軟なPLLを使用すると、複数の高速インターフェイス間の複雑なタイミングとプロトコル変換を管理できます。これらの機能により、テレコムインフラストラクチャと高帯域幅ネットワーキング機器に強く適合しています。

3。メモリコントローラーとデータ処理システム

EP2S60F672C4は、DDR、DDR2、RLDRAM II、QDR IIなどのさまざまな外部メモリインターフェイスをサポートしており、高帯域幅メモリコントローラーの設計に最適です。レイテンシを最小限に抑えて、高速でデータバッファリング、アドレス生成、および仲裁を処理できます。高速クロックネットワークと組み込みRAMブロックの組み合わせにより、大規模なデータストリームを効率的に管理できます。これにより、FPGAは画像処理、ビデオストリーミング、および重いデータスループットに依存する科学的計算プラットフォームに適しています。

4.カスタムロジックと組み込み加速

60,000を超えるロジック要素とリッチクロック管理により、FPGAは特定のアルゴリズム用のカスタマイズされたハードウェアアクセラレータをホストできます。設計者は、暗号化、プロトコル解析、リアルタイムコントロールループなど、CPUから計算集中タスクをオフロードするためにそれを使用します。また、複数の機能ブロックを統合して、複雑なSOCのような設計に適しています。この柔軟性により、産業自動化、セキュリティシステム、航空宇宙制御ユニットなどのアプリケーションで価値があります。

5。プロトタイピングと教育開発プラットフォーム

EP2S60デバイスは、プロトタイピング、テスト、および学術研究に使用されるFPGA開発キットによく見られます。ロジック容量、I/Oカウント、およびDSP機能のバランスにより、エンジニアと学生は単一のチップで完全なシステムを実装および検証することができます。デジタルデザインの迅速な反復をサポートし、ASIC開発にコミットする前にハードウェア検証を可能にします。多くの大学やR&Dラボでは、高度なデジタル設計と信号処理の概念を教えるために使用しています。

EP2S60F672C4同様の部品

|

仕様 |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

家族 /シリーズ |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

ロジック要素(LE) |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

|

施し |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

|

パッケージ |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

スピードグレード |

C4(STD) |

C3(より速い) |

C5(より速い) |

C5(より速い) |

I4(STD) |

I3(より速い) |

|

温度グレード |

コマーシャル(0〜70°C) |

コマーシャル |

コマーシャル |

コマーシャル |

産業(-40〜100°C) |

産業(-40〜100°C) |

|

I/Oピン |

492 |

492 |

492 |

492 |

492 |

492 |

|

オンチップメモリ |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

|

コア電圧 |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

|

重要な違い |

ベースラインの商業速度 |

C3スピードビン、リードフリー「N」 |

高速ビン |

高速ビン、「n」バリアント |

産業温度、同じ密度 |

産業、より速い速度、鉛フリー |

EP2S60F672C4プログラミング手順

デザインでEP2S60F672C4 FPGAを使用する前に、コンパイルされたビットストリームで適切に構成する必要があります。このプロセスには、プログラミングファイルの準備、ハードウェアインターフェイスのセットアップ、およびパワーアップ時に構成が正しくロードされるようにすることが含まれます。

ステップ1:デザインを作成してコンパイルします

Intel Quartus IIソフトウェアを使用して、ロジックデザインを開発することから始めます。設計を完了したら、それをコンパイルして、EP2S60F672C4デバイス用に特にプログラミングファイル(.sofまたは.pof)を生成します。コンピレーションプロセスは、タイミング、ピンの割り当て、リソースの使用をチェックして、FPGAのアーキテクチャに設計が適合するようにします。コンパイルされると、ビットストリームはデバイス構成の準備ができています。

ステップ2:プログラミングハードウェアをセットアップします

次に、PCとFPGAボードの間の物理プログラミングインターフェイスを準備します。通常、これには、USB-Blasterまたは互換性のあるJTAGケーブルをデバイスのJTAGポートに接続することが含まれます。Quartus IIがプログラマーを認識し、ターゲットデバイスが正しく検出されていることを確認する必要があります。このステップにより、構成プロセスを開始する前に安定した通信が保証されます。

ステップ3:プログラミングファイルをデバイスにロードします

Quartus IIプログラマーツールを使用して、コンパイルされた.sofまたは.pofファイルを追加し、検出されたデバイスリストからEP2S60F672C4を選択します。次に、プログラミングシーケンスを開始します。このシーケンスでは、ビットストリームが転送され、FPGAのSRAM構成セルにロードされます。成功した構成を確認するには、進行状況バーとステータスメッセージを監視する必要があります。完了すると、FPGAはすぐにプログラムされたロジックの実行を開始します。

ステップ4:構成と操作を確認します

プログラミング後、デバイスが意図したとおりに機能していることを確認します。Quartus IIは、設計が正しくロードされていることを確認するために、構成CRCとステータス信号を確認するための検証オプションを提供します。また、I/O機能をテストしたり、機能的なシミュレーションを実行してシステムの動作を確認することもできます。この最後のステップにより、設計が完全に動作し、ハードウェアで安定していることを保証します。

EP2S60F672C4の利点と短所

利点

•複雑な設計の高い論理密度

•パフォーマンスとコストの比率が良好です

•同じ家族内での簡単な移行

•安定した成熟した開発ツール

•産業用で実証された信頼性

短所

•陳腐化し、ソースが難しくなります

•新しいFPGAよりも高い消費電力

•最新の高速トランシーバーはありません

•高い利用時のより困難なタイミング閉鎖

•将来のプロトコルの限られたスケーラビリティ

EP2S60F672C4パッケージングの寸法

|

タイプ |

パラメーター |

|

パッケージタイプ |

672-FBGA(Fineline BGA) |

|

ボディサイズ(L×W) |

27.00 mm×27.00 mm |

|

合計パッケージの高さ(a) |

最大3.50 mm |

|

スタンドオフの高さ(A1) |

最小0.30 mm |

|

基質の厚さ(A2) |

最大3.00 mm |

|

ボールの直径(b) |

0.50 mm - 0.70 mm |

|

ボールピッチ(E) |

1.00 mm |

|

ボールの数 |

672 |

|

取り付けスタイル |

表面マウント |

|

パッケージの説明 |

FBGA、27×27 mmグリッド |

EP2S60F672C4メーカー

EP2S60F672C4 FPGAは製造されています Altera Corporation、プログラム可能なロジックデバイスの主要な先駆者。2015年、Alteraが買収されました インテル、そして現在、製品はIntelのプログラム可能なソリューショングループ(PSG)に該当し、Alteraの確立されたFPGAファミリーをサポートおよび供給し続けています。Intelは、Legacy製品ポートフォリオの一部としてStratix IIラインを維持し、産業および通信アプリケーションのドキュメント、ツールサポート、および長期的な可用性を確保します。

結論

EP2S60F672C4は、高い論理密度、柔軟なメモリアーキテクチャ、および堅牢なI/O機能を組み合わせて、複雑なデジタルシステムをサポートします。ALMベースの設計、Trimatrix™メモリ、DSPブロック、およびクロック管理機能により、要求の厳しいアプリケーションの効率的な実装が可能になります。実証済みの信頼性と成熟した開発サポートを提供しますが、新しいFPGA世代と比較して、陳腐化や最新のトランシーバーの欠如などの制限に直面しています。全体として、そのバランスの取れたパフォーマンスと汎用性により、信号処理、通信、データ処理、およびプロトタイピングアプリケーションのための確かな選択肢があります。

データシートPDF

EP2S60F672C4データシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1。EP2S60F672C4は、最新のDDRメモリインターフェイスで動作できますか?

はい、DDR、DDR2、QDR II、およびRLDRAM IIインターフェイスをサポートしています。これは、多くの一般的な外部メモリ標準をカバーしています。これにより、高帯域幅のデータ処理アプリケーションに適しています。

2。EP2S60F672C4には特別な取り扱いまたはストレージが必要ですか?

はい、他のBGAパッケージ化されたコンポーネントと同様に、水分制御パッケージに保管し、ESD保護で処理する必要があります。適切な貯蔵慣行に従うことで、アセンブリ中にはんだ付け性とデバイスの信頼性を維持するのに役立ちます。

3. EP2S60F672C4設計の消費電力をどのように削減できますか?

ロジックの使用率、ゲート未使用のクロック、可能な限り低いI/O電圧を最適化し、Quartus IIの電力認識合成オプションを活用して、全体的なパワードローを最小限に抑えることができます。

4. EP2S60F672C4にはどのようなプログラミングツールが必要ですか?

デバイスを構成するためのUSB-Blasterまたは互換性のあるJTAGケーブルとともに、設計、コンパイル、プログラミング用のIntel Quartus IIソフトウェアが必要です。

5。EP2S60F672C4は、フィールド内の更新またはリモート再構成をサポートしていますか?

はい、AESベースのビットストリーム暗号化とリモート再構成をサポートしているため、FPGAを物理的に交換せずにシステムを安全に更新できます。

LFXP6C-3FN256C格子半導体に関するすべて

10/6/2025で公開されています

XC2C256-7TQ144C CPLD:ピンアウト、機能、プログラミング、およびデータシートガイド

10/3/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/18/8000で公開されています 147780

-

USB-Cピンアウトと機能

04/18/2000で公開されています 112047

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/18/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/18/0400で公開されています 83806

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79607

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66986

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63113

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63048

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54097

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52199