EPF6016ATC144-2N FPGA:機能、プログラミング、アプリケーション、および代替案

このガイドは、FPGAと呼ばれるチップのタイプであるEPF6016ATC144-2Nに関するすべてです。デジタルシステムで使用されており、柔軟で更新しやすいものです。このガイドでは、チップが何をしているか、それがどのように機能するか、その主要な部分と機能、それを使用してプログラムする方法、使用できる場所、そしてそれが今日でも良い選択である理由を説明しています。カタログ

EPF6016ATC144-2Nとは何ですか?

EPF6016ATC144-2N 現在はIntelの一部であるAlteraが開発したFlex 6000 FPGAファミリーのメンバーです。SRAMベースの再プログラム可能なロジック上に構築されたこのデバイスは、中密度のデジタルロジックアプリケーションで柔軟性のために設計されています。ロジックアレイブロック(ラボ)と高速相互接続マトリックスを組み合わせて、効率的なリソースの使用率と高速信号ルーティングを提供するOptiflexアーキテクチャを活用します。EPF6016ATC144-2Nは、システム内の再構成をサポートしているため、展開後の更新や変更を必要とするデザインに最適です。Flex 6000シリーズの一部として、開発サイクルを簡素化しながら、従来のゲートアレイを交換するための費用対効果の高いソリューションを提供します。

EPF6016ATC144-2Nをお探しですか?現在の在庫、リードタイム、価格を確認するには、お問い合わせください。

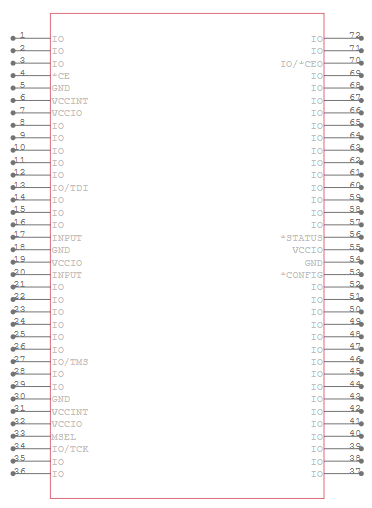

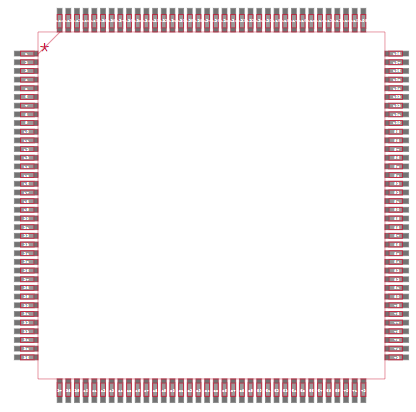

EPF6016ATC144-2N CADモデル

EPF6016ATC144-2Nシンボル

EPF6016ATC144-2Nフットプリント

EPF6016ATC144-2N 3Dモデル

EPF6016ATC144-2N機能

• ロジック容量

EPF6016ATC144-2Nは、132のロジックアレイブロック(LAB)にわたって1,320ロジック要素(LES)を使用して実装された約16,000のシステムゲートを提供します。これにより、中距離FPGAアプリケーションに適した中程度の複雑さが提供されます。

• I/Oピン

最大117のユーザー構成I/Oピンをサポートします。これらのピンは、さまざまなシステムコンポーネントおよび外部デバイスへの柔軟な接続を可能にします。

• コア電圧

コアは3.0Vから3.6Vの機能範囲で3.3Vで動作します。これにより、標準の低電圧デジタルシステムとの互換性が可能になります。

• I/O電圧

マルチボルトI/O機能は、3.3Vまたは2.5Vレベルを使用してデバイスとのインターフェースをサポートします。これにより、混合電圧環境への統合が簡素化されます。

• 動作温度

標準動作接合温度範囲は0°C〜 +85°Cです。これは、典型的な商業および産業環境をサポートします。

• 供給電流

通常の動作中に約5MAを引き、スタンバイモードでは0.5MA未満です。これは、エネルギー志向のデザインの電力を節約するのに役立ちます。

• クロック速度(スピードグレード–2n)

–2速度グレードでは、約166MHzまでの内部ロジック周波数を達成します。これにより、信号処理または制御ロジックの迅速な計算が可能になります。

• 建築

AlteraのOptiflexアーキテクチャに基づいて、専用のルーティングリソースを備えたLUTベースのロジックを使用します。このアーキテクチャは、高い論理密度と効率的なパフォーマンスを提供します。

• FastTrack InterConnect

FastTrackルーティンググリッドは、低遅延の信号パスを可能にし、ロジックブロック全体の高速データ転送をサポートします。これは、一貫したタイミングとパフォーマンスに貢献します。

• 回路の再構成

SRAMベースのロジック構成を使用して、FPGAをシステム内で再プログラムできるようにします。これは、削除せずに設計の更新または動的なハードウェアの適応をサポートします。

• JTAG境界スキャン

このデバイスには、IEEE 1149.1に準拠したJTAG境界スキャンロジックが含まれます。これにより、ボードと相互接続のデバッグとシステム内のテスト可能性が容易になります。

• ホットソケットのサポート

3.3Vシステムで電源を入れながら、安全に挿入または削除できます。この機能は、モジュラーまたはサービス可能なハードウェアプラットフォームで役立ちます。

• 機能テスト

各ユニットは、出荷前に完全に機能的にテストされています。これにより、開発中にユーザー定義のテストベクトルの必要性が確保され、排除されます。

• PCI互換性

このデバイスは、5V操作用のPCIローカルバスリビジョン2.2と互換性があります。これにより、レガシーPCIベースの埋め込みシステムで使用できます。

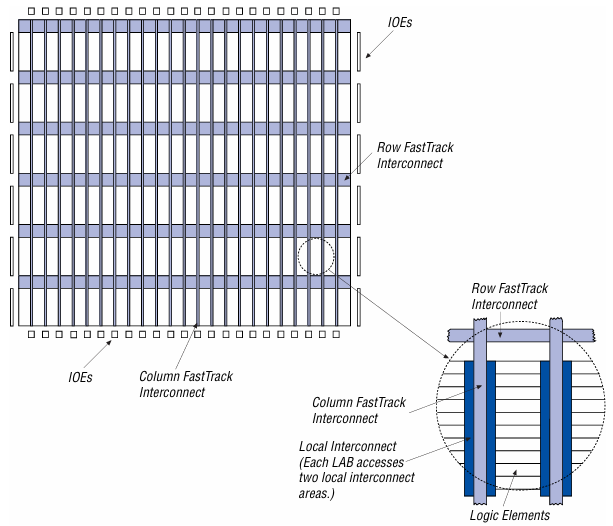

Optiflexアーキテクチャブロック図

この図は、FPGAの内部部分がどのように編成され、接続されているかを示しています。中央にはロジックアレイブロック(ラボ)があり、これらはチップのメインビルディングユニットです。各ラボには、ロジックゲートやフリップフロップなどの基本的なデジタル操作を実行するいくつかのロジック要素(LE)が含まれています。ラボはローカルの相互接続で接続されているため、各ブロック内のロジックが効率的に連携できるようになります。チップ全体のより広範な通信のために、ラボは行と列のFastTrackインターコネクトにリンクし、データをチップのある部分から別の部分に迅速に移動できる高速信号パスを低下させます。図の外側のエッジの周りには、入出力要素(IOES)があります。これらは、FPGAの内部ロジックを、チップのロジックレベルと他のハードウェアで使用する電圧レベルを変換することにより、外部デバイスに接続します。モジュラーブロックと高速ルーティングパスを備えたこのレイアウトは、Optiflexアーキテクチャの柔軟性とパフォーマンスの焦点を反映しています。

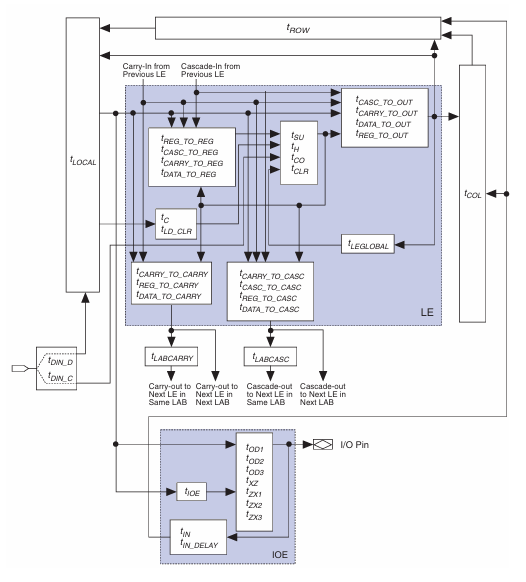

フレックス6000タイミングモデル

Flex 6000タイミングモデルは、FPGAを通過する際に信号がどのように移動し、遅延しているかを示しています。モデルの中心には、特定のタイミングでデータと制御信号を処理するロジック要素(LE)があります。各LEは、T_DATA_TO_REGやT_REG_TO_OUTのようなタイミングパスに接続します。これにより、信号が入力、処理され、ロジックを終了するのにかかる時間が定義されます。

LESの隣には、Lab CarryとLab Cascadeと呼ばれる特別なパスがあります。これらにより、信号は同じブロック内のロジック要素間で水平に移動し、追加や比較などの高速操作をサポートします。これらのパスには、これらの操作中の遅延を測定するために、T_CARRY_TO_REGやT_CASC_TO_OUTなどの独自のタイミング値もあります。

図の下部では、入力/出力要素(IOE)がチップに出入りする信号を処理します。これらには、外部デバイスからデータを受信する際のバリエーションを説明するT_IN_DELAYのような遅延ポイントが含まれています。

このモデルには、異なるレベル(T_Local、T_ROW、T_COL、およびT_GLOBAL)のルーティングパスも含まれます。これらのパスは、チップのさまざまな部分での遅延を理解して管理するのに役立ち、パフォーマンスとタイミングの目標を達成しやすくなります。

EPF6016ATC144-2N仕様

|

タイプ |

パラメーター |

|

メーカー |

アルテラ/インテル |

|

シリーズ |

フレックス6000 |

|

パッケージング |

トレイ |

|

パーツステータス |

廃止 |

|

ラボ/CLBの数 |

132 |

|

ロジック要素/セルの数 |

1320 |

|

I/Oの数 |

117 |

|

ゲートの数 |

16000 |

|

電圧 - 供給 |

3V〜3.6V |

|

取り付けタイプ |

表面マウント |

|

動作温度 |

0°C〜85°C(TJ) |

|

パッケージ /ケース |

144-LQFP |

|

サプライヤーデバイスパッケージ |

144-TQFP(20x20) |

|

基本製品番号 |

EPF6016 |

EPF6016ATC144-2Nアプリケーション

1.デジタル信号処理(DSP)タスク

1,320のロジック要素と高速相互接続により、EPF6016ATC144-2Nは、小規模からミッドレンジのデジタル信号処理機能の実装をサポートしています。カスタムFIRフィルター、FFTコア、または信号変換のための並列算術ロジックを作成するために使用できます。専用のDSPブロックまたは組み込みの乗数はありませんが、その汎用ロジックは、コントロールまたは通信システムの埋め込みオーディオ処理、センサーデータフィルタリング、および波形形状に適した繰り返しの多目的蓄積操作を処理できます。

2.埋め込み制御と産業の自動化

このデバイスは、産業環境に埋め込まれた制御アプリケーションに適しています。混合電圧I/O(2.5 Vおよび3.3 V)と編成する能力、標準的な商業温度(0〜85°C)の下での安定した動作、およびホットソケットのサポートにより、プログラム可能なロジックコントローラー(PLCS)、モーターコントロール単位、計装インターフェース、および汎用自動化機器への統合に信頼性が高くなります。再構成性により、ハードウェアを置き換えることなくロジックを更新できる長期的な製品の柔軟性が可能になります。

3.通信プロトコルブリッジングとインターフェイスロジック

マルチボルトI/Oサポートと効率的なルーティングネットワークのおかげで、EPF6016ATC144-2Nを使用して、カスタム通信インターフェイスとプロトコルコンバーターを実装できます。UART、SPIコントローラー、または並列バス翻訳者を構築して、不一致のデジタルシステム間の相互作用を可能にすることができます。中程度のI/Oカウント(117 GPIO)および内部クロック管理は、時間に敏感なシグナル伝達をサポートしているため、ネットワーキング機器、レガシーバスエミュレーション、または大規模なデータ通信システムの接着剤ロジック要素に適しています。

4.ボードレベルのテスト、デバッグ、および検証

組み込みのJTAG境界スキャン機能(IEEE 1149.1準拠)を備えたEPF6016ATC144-2Nは、外部ロジックプローブや邪魔な診断を必要とせずに高度なボードレベルのテストをサポートしています。I/Oの接続を検証し、オープンサーキットまたはショートサーキットを検出し、生産またはフィールドメンテナンス中にシステム内チェックを実行できます。この機能は、複雑な多層PCBまたはテストポイントへの従来のアクセスが制限または非現実的なシステムで役立ちます。

EPF6016ATC144-2N同様の部品

|

特徴 |

EPF6016ATC100-1 |

EPF6016ATC100-3N |

EPF6016ATC144-3N |

|

メーカー |

アルター |

Intel(Altera Legacy) |

Intel(Altera Legacy) |

|

家族 |

フレックス6000 |

フレックス6000 |

フレックス6000 |

|

ロジック要素(LES) |

1,320 |

1,320 |

1,320 |

|

ゲートカウント(約) |

16,000 |

16,000 |

16,000 |

|

パッケージ |

100ピンTQFP |

100ピンTQFP |

144ピンTQFP |

|

ユーザーI/Oピン |

81 |

81 |

117 |

|

スピードグレード |

-1(標準) |

-3n(高速) |

-3n(高速) |

|

最大クロック周波数 |

低い(通常は〜100 MHz) |

より高い(最大166 MHz) |

より高い(最大166 MHz) |

|

構成タイプ |

SRAMベース |

SRAMベース |

SRAMベース |

|

電源電圧 |

3.3 v |

3.3 v |

3.3 v |

|

ホットソケット |

はい |

はい |

はい |

|

JTAG/境界スキャン |

はい |

はい |

はい |

|

アプリケーション |

基本的なロジック、コンパクトデザイン |

より高速な制御ロジック、コンパクト |

高性能システム、より多くのI/O |

|

可用性 |

廃止 |

廃止 |

廃止 |

EPF6016ATC144-2Nプログラミング手順

1.構成モードを選択します

EPF6016ATC144-2Nは、SRAMベースの構成をサポートしています。つまり、すべてのパワーアップでプログラミングが必要です。このデバイスは、いくつかの構成スキーム、最も一般的にパッシブシリアル(PS)とパッシブ平行非同期(PPA)を許可します。構成モードは、MSELピンの接続方法によって決定されます。たとえば、MSELが低い場合、デバイスはデータが外部EEPROM(EPC1など)またはダウンロードケーブルを介して連続的に送信されることを期待しています。正しい構成方法を選択すると、システム設計、自動ブートアップのEEPROMベース、またはプロトタイプとテスト用のケーブルベースに依存します。

2. FPGA設計をコンパイルし、プログラミングファイルを生成します

FPGAをプログラムするには、最初にIntelのQuartusまたはLegacy Max+Plus IIデザインソフトウェアを使用してハードウェア設計を作成する必要があります。コンパイル後、ツールは構成されたロジックを表すSOF(SRAMオブジェクトファイル)を生成します。このSOFは、選択した構成方法と互換性のあるフォーマットに変換する必要があります。

•EEPROMデバイス用の.RBFまたは.POF(例:EPC1)。

•マイクロコントローラーまたは並列荷重用の.ttfまたは.hex。

変換は、設計ソフトウェアの組み込みファイルコンバーターユーティリティを使用して行われます。この手順により、FPGAが解釈できるようにビットストリームが正しくフォーマットされます。

3.構成メモリをプログラムします(EEPROMを使用する場合)

EPC1のようなシリアル構成デバイスが使用されるアプリケーションでは、次のステップは構成データをEEPROMにロードすることです。これは通常、デスクトッププログラミングツール(Max+Plus IIプログラマーまたはQuartusプログラマーなど)を使用して行われます。このプロセスでは、EEPROMをプログラミングソケットに配置するか、回路内で接続し、適切なプログラミングファイル(通常.POFまたは.RBF)をロードし、プログラムサイクルを開始します。プログラムされると、EEPROMはシステムが電力を供給するたびに構成データをFPGAに自動的に提供し、手動の再プログラミングの必要性を排除します。

4.ダウンロードケーブルを使用して構成(パッシブシリアル)

EEPROMベースのブートアップに代わるものは、FPGAを直接構成するためにダウンロードケーブル(USB-BlasterやByteBlasterなど)を使用することです。この方法では、ケーブルをPCに接続し、FPGAのNCONFIG、DCLK、データ、およびconf_doneピンを接続します。Quartusプログラマーを使用して、nconfigを低くパルスして開始する構成プロセスを開始します。このツールは、DCLKでクロックされたデータラインを介して設定データをシリアルに送信します。CONF_DONEが高くなったときにプロセスが完了し、構成が成功し、デバイスのユーザーモードへの移行が示されます。

5.マイクロコントローラーを使用して構成(パッシブシリアル/パラレル)

システムが埋め込まれたマイクロコントローラーを使用している場合、FPGAの構成マスターとしても機能します。このセットアップでは、マイクロコントローラーはNCONFIGを低く、FPGAをリセットし、DCLKを切り替えながら構成ビットストリームをデータからシフトします。タイミング要件を尊重する必要があります。クロックの前のデータセットアップ時間とその後の時間を保持する必要があります。マイクロコントローラーは、NSTATUSおよびconf_doneピンを監視して、構成エラーを検出したり、正常に完了したりすることができます。この方法は、構成プロセスを完全に制御し、フィールドでの動的な更新をサポートします。

6.構成信号を監視します

構成プロセス中、FPGAはステータスピンを介してフィードバックを提供します。

•NSTATUSはエラー検出を示します。障害が発生すると低くなります(たとえば、CRCエラーやタイミング違反)。

•すべての構成ビットが正常に読み込まれ、検証されると、conf_doneが高くなります。

NSTATUSが高いままであり、CONF_DONEがシーケンスの最後に高い遷移の場合、デバイスはユーザーモードを自動的に入力し、ユーザー定義のロジックがアクティブになります。この信号監視は、プログラミングプロセスが正常に完了するようにするために重要です。

7.必要に応じて再構成を実行します

EPF6016ATC144-2NはSRAMベースであるため、NCONFIG PIN LOWを切り替えることにより、いつでも再構成できます。これにより、デバイスをリセットして構成サイクルを再起動します。この機能により、物理的な交換なしの操作中に柔軟なシステムの更新と変更が可能になります。インサーキット中に再構成する能力は、展開後の冗長性、動的関数のスワッピング、または展開後のバグの修正もサポートします。これにより、デバイスは適応性または寿命を必要とするアプリケーションに非常に適しています。

8.タイミングと電気の要件を観察します

EPF6016ATC144-2Nをプログラミングするには、電気およびタイミングの制約にも注意が必要です。構成クロック(DCLK)は、周波数制限を満たす必要があります(たとえば、標準シリアルモードでは通常、最大10 MHz)。デバイスは、内部のパワーオンリセットが安定するために電源を上げた後、短い遅延(約200ミリ秒)が必要です。さらに、すべての構成信号はクリーンで、ノイズがなく、適切に終了する必要があります。ホットソケットを使用する場合は、信号の完全性と電力とI/Oの適切なシーケンスを確保するために注意する必要があります。

EPF6016ATC144-2N利点

• 複数の複数の設計に費用対効果が高い

EPF6016ATC144-2Nは、手頃な価格と機能性のバランスをとっているため、固定ロジックよりも柔軟性を必要とするデザインに最適ですが、高級FPGAの費用や電力オーバーヘッドを正当化しないでください。

• 簡略化されたPCB設計と統合

多くの場合、ファインピッチBGAパッケージを必要とする高密度FPGAと比較して、EPF6016ATC144-2Nには標準の144ピンTQFPパッケージがあります。このパッケージは、PCBの設計と製造の両方を簡素化します。これは、高度なレイアウトツール、マイクロバイア、または高層高層カウントボードの必要性を回避するためです。また、手持ち式または基本的なリワークを促進します。これは、アセンブリ能力が限られている小規模なチームやラボにとって有益です。

• 展開中の陳腐化の低リスク

Legacy Industrial Applicationsでの長年のサポートにより、EPF6016ATC144-2Nは多くの流通市場で引き続き利用可能であり、Quartus IIやMax+Plus IIなどの設計ソフトウェアで依然として広くサポートされています。ファクトリーオートメーション、測定システム、テレコムモジュールなどの長距離製品を維持している企業の場合、これにより、より新しい、より複雑なFPGAの周りにハードウェアを再設計する必要なく、既知の優れたシリコンへの継続的なアクセスが保証されます。

• 信頼できる動作

緊密なマージンで動作し、電力と温度の変動に敏感ないくつかの新しい高性能FPGAとは異なり、EPF6016ATC144-2Nは堅牢で一般的な環境変動に耐性があります。商業温度範囲で快適に動作し、ホットソケットをサポートするため、モジュラーまたはサービス可能なシステムで信頼性が高くなります。この信頼性により、時間とさまざまな条件下で一貫したパフォーマンスを必要とするシステムにとって実用的な選択肢になります。

• 長期設計の安定性

長期的な可用性と設計フリーズが最先端のパフォーマンスよりも重要であるシナリオでは、このデバイスは堅実な候補です。ロジックが検証され、構成ファイルがロックダウンされると、システム全体が何十年もの間、何年も変わらないままになります。これは、新しい部品の再設計が高価または非現実的である航空宇宙、輸送、および軍事アプリケーションの大きな利点です。

EPF6016ATC144-2Nパッケージングの寸法

パッケージタイプ:TQFP-144(薄いクアッドフラットパッケージ)

体の大きさ:20 mm×20 mm

ピンピッチ:0.5 mm

ピンカウント:144ピン

パッケージの高さ:1.0 mm

リードフレームタイプ:ガルウィングは4つの側面すべてをリードします

取り付けタイプ:Surface-Mount(SMT)

EPF6016ATC144-2Nメーカー

EPF6016ATC144-2Nは元々製造されていました Altera Corporation、フィールドプログラム可能なゲートアレイ(FPGA)の開発の先駆者。2015年、Alteraが買収されました Intel Corporationそして、このデバイスは現在、Intelのプログラム可能なSolutions Groupの下に正式にリストされており、AlteraのLegacy FPGA製品ラインを管理およびサポートしています。EPF6016ATC144-2Nは廃止された家族の一部ですが、Intelはこのデバイスの正式なメーカーおよびカストディアンであり、Intelブランディングの下でドキュメント、アーカイブサポート、ライフサイクル通知を維持しています。

結論

EPF6016ATC144-2Nは、さまざまなプロジェクトの柔軟で信頼できるFPGAです。かなりの量のロジック能力、多くの入出力ピン、および簡単なシステム内の更新を提供します。その設計は、混合電圧システム、高速データの動き、およびボードから削除せずに再プログラミングをサポートします。制御システム、信号処理、通信リンク、テスト機器などでよく使用されます。強力なサポート、長い可用性、シンプルなパッケージングにより、費用対効果の高い安定したソリューションが必要な賢明な選択肢のままです。

データシートPDF

EPF6016ATC144-2Nデータシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1.今日のEPF6016ATC144-2Nをプログラムするためにどのようなツールが必要ですか?

IntelのLegacy Quartus IIまたはMax+Plus IIソフトウェアを開発およびコンピレーションに使用できます。プログラミング用に、USB-BlasterケーブルやQuartusプログラマーなどのツールは、構成に互換性があり続けます。

2。EPF6016ATC144-2Nは、小規模生産の実行またはプロトタイピングに適していますか?

はい。TQFP-144パッケージにより、高度なアセンブリツールを必要とせずにプロトタイプが簡単になります。また、低コストと柔軟性が必要な小規模生産にも最適です。

3. EPF6016ATC144-2Nは、パフォーマンスの観点から新しいFPGAとどのように比較されますか?

最新のハイエンドFPGAほど機能が豊富ではありませんが、EPF6016ATC1444-2Nは、低電力消費とより単純な統合とともに中程度のロジックの複雑さのために信頼できるパフォーマンスを提供し、多くのアプリケーションで費用対効果が高くなります。

4.ライブシステムでEPF6016ATC144-2Nをホットプラグインするのは安全ですか?

はい。このFPGAは、3.3Vシステムのホットソケットをサポートし、ホストボードに電源を入れることなく挿入または削除できるようにします。これは、フィールドサービスやモジュラーハードウェア設計に最適です。

5.カスタムASICまたはCPLDソリューションよりもEPF6016ATC144-2Nを選択する必要があるのはなぜですか?

EPF6016ATC144-2Nは、ASICと比較して、開発サイクル、フィールド内の再プログラミング、前払いコストの削減をより高速に提供します。CPLDと比較して、スケーラブルで進化するデザインに最適な、より多くのロジック容量と柔軟なルーティングを提供します。

LC5768MC-75F256C CPLD:機能、仕様、利点、アプリケーション

07/10/2025で公開されています

MC7447AHX1000NBを開始します

07/10/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/19/8000で公開されています 147784

-

USB-Cピンアウトと機能

04/19/2000で公開されています 112077

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/19/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/19/0400で公開されています 83844

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79648

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 67019

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63138

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63071

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54099

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52229