EPM7160ELC84-15:データシート、機能、ピンアウト、プログラミング、アプリケーション

このガイドは、カスタムデジタルロジックサーキットの構築に役立つ特別なチップであるEPM7160ELC84-15に関するものです。JTAG接続を使用してプログラムしたり、システムに既にインストールされている間に更新することもできます。また、デザインを保護するためのセキュリティ機能もあります。この記事では、ピンのレイアウト、機能、用途、プログラム方法など、チップに関するすべてを説明します。機械、車、ネットワーク機器に取り組んでいるかどうかにかかわらず、このガイドは、このチップが役立つ理由を理解するのに役立ちます。カタログ

EPM7160ELC84-15概要

EPM7160ELC84-15 IntelのMax 7000シリーズのCPLDの一部であり、Alteraの高度な第2世代のMaxアーキテクチャを利用しています。ハイエンドCMOSテクノロジーで製造されたこれらのデバイスは、高密度および高性能デジタルロジック回路の実装に合わせて調整されています。このモデルは160個のマクロセルを備えており、約3,200個の使用可能なゲートを提供し、複雑なデジタルシステムのニーズに対応しています。典型的なピンからピンへの遅延15 nsで5V電源で動作し、最大175.4 MHzのカウンター速度が可能になり、迅速な信号処理と効率的なシステムパフォーマンスが確保されます。このCPLDは、IEEE STDに準拠した統合されたJTAGインターフェイスを介して、システム内プログラミングと再プログラミングの両方をサポートしています。1149.1、インストール後の柔軟性と更新の容易さ。また、知的財産を保護するための貴重な追加である構成データの不正なコピーを防ぐためのセキュリティビット機能も提供します。

あなたがあなたのビジネスが必要とするすべてを確保したいなら、今は私たちと一緒に一括注文をするのに最適な時期です。時間を節約し、コストを削減し、必要なものを正確に取得できるようになりました。

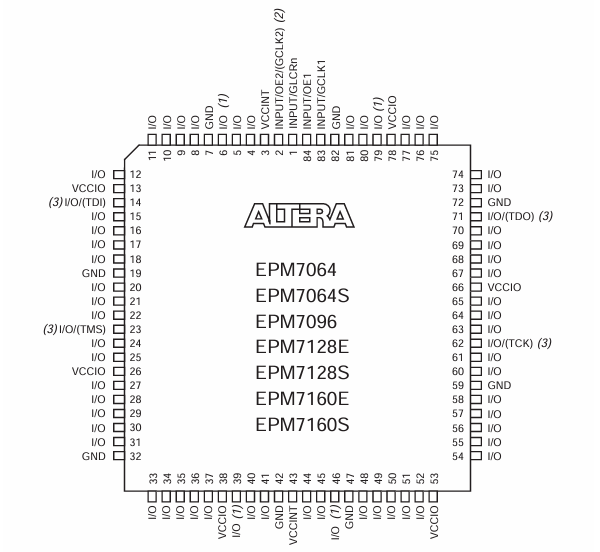

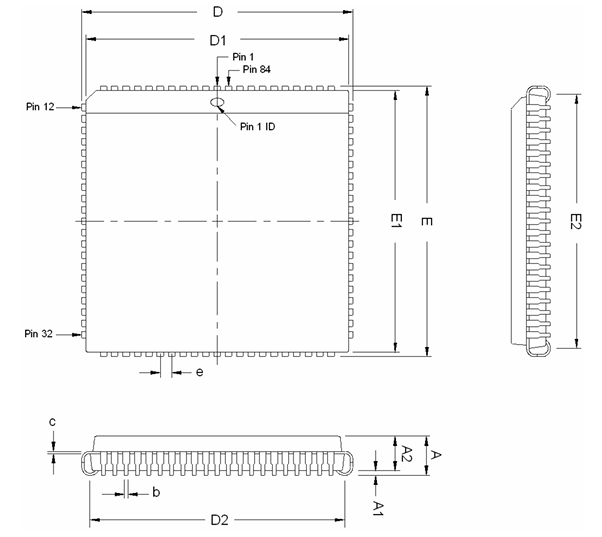

EPM7160ELC84-15ピンアウト図

のピンアウト図 EPM7160ELC84-15 デバイスは、PLCC(プラスチックリードチップキャリア)パッケージの84ピンの物理レイアウトと機能を示しています。図は正方形の構成を示しています。各ピンには、そのような機能を示す特定のラベルが割り当てられています。 I/o (入力/出力)、 GND (地面)、または vccio (I/Oの電源電圧)。Asとしてラベル付けされたピン I/o 回路内の他のデバイスとのインターフェースに使用される構成可能なデジタル入力または出力ラインを表します。 vccio ピンに電圧を供給します I/O銀行、 そして GND ピンは地上参照を提供します。特殊機能ピンには含まれます TDI、 TDO、 TMS、 そして TCK、に使用されます jtag プログラミングおよび境界スキャンテスト。さらに、ピンが好きです input1/clk1 そして input2/clk2 内部ロジックタイミングの指定されたクロックまたは制御信号入力です。

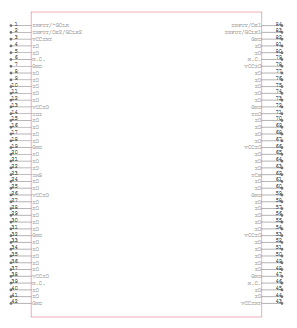

EPM7160ELC84-15 CADモデル

EPM7160ELC84-15シンボル

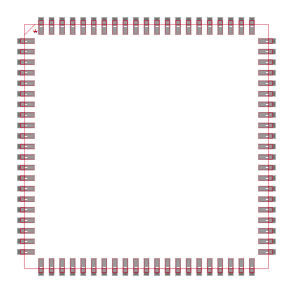

EPM7160ELC84-15フットプリント

EPM7160ELC84-15 3Dモデル

EPM7160ELC84-15機能

• 高密度ロジック:EPM7160ELC84-15は、160のマクロセルと約3,200の使用可能なゲートを提供しており、複雑なデジタルデザインに非常に適しています。この密度により、複数の関数を単一のデバイスに統合することができ、よりコンパクトで効率的な回路設計を促進します。

• 速いパフォーマンス:15 nsの最大伝播遅延と最大100 MHzまでの動作周波数をサポートする機能により、このCPLDは、時間に敏感なアプリケーションの迅速な信号処理と高速性能を保証します。

• システム内プログラマ性(ISP):組み込みのIEEE stdを備えています。1149.1(JTAG)インターフェイス、デバイスはシステム内プログラミングをサポートします。この機能により、デバイスをプログラムしてインストール後に再プログラムすることができ、物理的な交換を必要とせずに更新と機能の変更に柔軟性を提供します。

• MultiVolt™I/Oインターフェイス :Multivolt I/Oインターフェイスは、さまざまな動作電圧をサポートし、CPLDを5.0 V、3.3 V、および2.5 Vのロジックレベルと互換性があります。この機能により、デバイスは混合電圧システムで使用でき、さまざまな電子環境への適応性を高めることができます。

• 柔軟なI/O構成:汎用性の高いインターフェースオプションを提供する64のプログラム可能なI/Oピンを提供します。この柔軟性は、さまざまな入出力構成を必要とするアプリケーションにとって重要であり、幅広い接続性と機能をサポートしています。

• EEPROMベースのメモリ:構成ストレージにEEPROMテクノロジーを利用すると、CPLDは最大100回再プログラムできます。この非揮発性メモリは、信頼性とメンテナンスの容易さのために電源サイクル後でもデバイスが構成を保持することを保証します。

• セキュリティ機能:デバイスには、プログラムされたロジックへの不正アクセスを防ぎ、知的財産を保護し、改ざんの防止を防ぐセキュリティビットが含まれています。これは、セキュリティに敏感な環境でのアプリケーションに適しています。

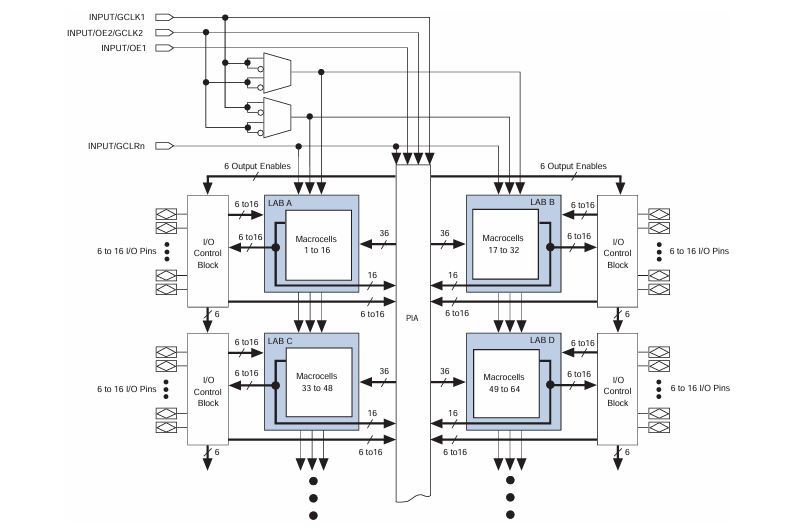

EPM7160ELC84-15ブロック図

のブロック図 EPM7160ELC84-15、4つで構成される適切に構成された内部アーキテクチャを表します ロジックアレイブロック(ラボ) ラベル付き a、 b、 c、 そして d。各ラボには含まれています 16のマクロセル、合計を作成します 64マクロセル、ロジック関数を作成するための建物ユニットです。これらのマクロセルは、プログラム可能な相互接続と制御信号を使用して、組み合わせロジックまたは登録ロジックを実装できます。中央で、 プログラム可能な相互接続配列(PIA) 通信バックボーンとして機能し、間で信号の柔軟なルーティングを可能にします ラボ そして I/o ピン。各ラボは、36の入力ラインと16の出力ラインでPIAに接続し、高度なロジック相互接続性を確保します。周辺の周り、 I/Oコントロールブロック 入力信号と出力信号を管理し、外部システムと直接インターフェースする6〜16個のI/Oピンを片側に提供します。また、同期して集中したロジック制御のために、すべてのラボに分布した、クロック(GCLK1、GCLK2)、出力イネーブル(OE1)、クリア(GCLRN)などのグローバルコントロール信号も表示されます。これらの信号は、マルチプレクサを介してルーティングして、設計の柔軟性と効率を提供できます。

EPM7160ELC84-15仕様

|

タイプ |

パラメーター |

|

メーカー |

アルテラ/インテル |

|

シリーズ |

MAX®7000 |

|

パッケージング |

チューブ |

|

パーツステータス |

廃止 |

|

プログラム可能なタイプ |

EE pld |

|

遅延時間TPD(1)最大 |

15 ns |

|

電圧供給 - 内部 |

4.75V〜5.25V |

|

ロジック要素/ブロックの数 |

10 |

|

マクロセルの数 |

160 |

|

ゲートの数 |

3200 |

|

I/Oの数 |

64 |

|

動作温度 |

0°C〜70°C(TA) |

|

取り付けタイプ |

表面マウント |

|

パッケージ /ケース |

84-lcc(j-lead) |

|

サプライヤーデバイスパッケージ |

84-PLCC(29.31x29.31) |

|

基本製品番号 |

EPM7160 |

EPM7160ELC84-15アプリケーション

産業用自動化

産業用自動化では、EPM7160ELC84-15を利用して、プログラマブルロジックコントローラー(PLC)、モーターコントローラー、およびセンサーインターフェイス内のロジックを制御します。複雑なロジック操作と高速I/Oスイッチングを処理する能力により、正確な制御とタイミングを必要とする自動化タスクに最適です。

組み込みシステム

このCPLDは、スペースと電力効率が重要な埋め込みシステムに役立ちます。ロボット工学、モノのインターネット(IoT)デバイス、およびコンシューマーエレクトロニクスにアプリケーションが見つかります。この場合、そのプログラマ性により、特定の機能要件に対するカスタマイズと適応性が可能になります。

通信

このデバイスは、タイミング、データルーティング、プロトコル処理を管理するためのルーターやスイッチなどの通信機器で採用されています。高速パフォーマンスと異なる電圧レベルで動作する能力により、信頼性と高いデータスループットを要求するネットワークインフラストラクチャに適しています。

自動車電子機器

自動車セクター内で、EPM7160ELC84-15は、インフォテインメントシステム、ボディコントロールモジュール、およびエンジン管理ユニットのアプリケーションをサポートしています。CPLDの堅牢性と幅広い入出力電圧のサポートにより、自動車環境の厳しい条件で確実に機能することができます。

医療機器

CPLDは、特に診断機器と患者監視システムにも適用されます。さまざまな環境条件下でのセキュリティ機能と安定した操作により、敏感で医療アプリケーションを安全かつ効率的に処理できるようになります。

EPM7160ELC84-15同様の部品

EPM7160ELC84-15プログラミング手順

IntelのMax 7000シリーズのCPLDであるEPM7160ELC84-15のプログラミングには、仕様に応じてデバイスが機能するように構造化されたプロセスが含まれます。このCPLDのプログラミングに伴う手順は次のとおりです。

1.設計エントリ:まず、VHDLやVerilogなどのハードウェア説明言語(HDL)、またはデジタルロジックデザインを作成するためのグラフィカルな概略的キャプチャツールを使用します。この最初のステップは、CPLDで実装する機能の基礎を築きます。AlteraのQuartus IIやMax+Plus IIなど、Max 7000シリーズと互換性のあるデザインソフトウェアを使用して、設計をコーディング、コンパイル、シミュレーションするためのツールを提供します。

2.編集とシミュレーション:設計をコンパイルして、HDLコードまたは回路図をCPLDが実行できるバイナリ形式に変換します。このステップでは、構文エラーもチェックし、ロジックが設計要件を満たしていることを確認します。コンパイルされたデザインをシミュレートして、その機能を検証します。これには、デザインに対してテストケースを実行してロジックとタイミングを検証し、物理デバイスにプログラムされる前に予想どおりに動作するようにします。

3.プログラミングハードウェアのセットアップ:EPM7160ELC84-15を適切なプログラミングハードウェアに接続します。これには、byteblastermv、masterblaster、またはusb-blasterなどのデバイスでJTAGインターフェイスを設定することが含まれます。CPLDが適切に電源を供給し、通常5.0 V電源を使用して、プログラミング用に正しい構成モードでセットアップされていることを確認してください。

4.プログラミングプロセス:プログラミングソフトウェア(Quartus IIプログラマーなど)を開き、JTAGインターフェイスを介してEPM7160ELC84-15を認識するように構成します。適切なプログラミングファイル(.pofまたは.sof)をソフトウェアにロードします。これらのファイルには、CPLDの構成に必要なコンパイルされた設計データが含まれています。ソフトウェア内のプログラミングコマンドを実行して、設計をCPLDに転送します。エラーのプロセスを監視し、プログラミングの完了が成功したことを確認します。

5.検証:プログラミングが完了したら、検証プロセスを実行して、CPLDが意図したアプリケーション内で正しく動作するようにします。これには、CPLDが実装されている実際のシステム内で、境界スキャンテストまたは機能テストの実施が含まれる場合があります。すべての機能が設計どおりに実行され、デバイスがシステム内の他のコンポーネントと正しく対話することを確認します。

EPM7160ELC84-15利点

費用対効果

EPM7160ELC84-15は、新しいCPLDまたはFPGAに関連付けられた高値タグなしで複雑なロジック機能を必要とするための費用対効果の高いソリューションです。これにより、予算に敏感なプロジェクトや教育的または小規模な産業用アプリケーションにとって魅力的です。

不揮発性構成

EEPROMテクノロジーを利用して、EPM7160ELC84-15は、電源がオフになった場合でも、プログラムされた構成を保持します。この非揮発性により、パワーサイクル全体のパフォーマンスのデバイスの信頼性と一貫性が保証され、外部の不揮発性メモリコンポーネントの必要性が排除されます。

広い動作電圧範囲

このデバイスは、4.75 V〜5.25 Vの幅広い動作電圧範囲をサポートし、さまざまな電源を収容し、古いシステムと新しいシステム設計の両方との互換性を確保します。この汎用性は、システムコンポーネントが同じ標準電圧レベルを共有できない混合電圧環境で有益です。

信頼できるパフォーマンス

このデバイスは、15 nsの伝播遅延と最大100 MHzの動作周波数をサポートする信頼性の高いパフォーマンスを提供します。これにより、ロジック操作のタイムリーかつ効率的な処理が保証され、電気通信、自動車電子機器、および産業制御システムの時間に敏感なアプリケーションに適しています。

EPM7160ELC84-15パッケージングの寸法

パッケージアウトラインディメンションテーブル

|

シンボル |

インチ |

||

|

分 |

nom。 |

マックス。 |

|

|

a |

0.165 |

0.172 |

0.18 |

|

A1 |

0.02 |

- |

- |

|

A2 |

0.150タイプ |

||

|

d |

1.185 |

1.190 |

1.195 |

|

D1 |

1.150 |

1.154 |

1.158 |

|

D2 |

1.082 |

1.110 |

1.138 |

|

e |

1.185 |

1.190 |

1.195 |

|

E1 |

1.150 |

1.154 |

1.158 |

|

E2 |

1.082 |

1.110 |

1.138 |

|

b |

0.013 |

- |

0.021 |

|

c |

0.008 Typ |

||

|

e |

0.050タイプ |

||

パッケージの概要

EPM7160ELC84-15メーカー

EPM7160ELC84-15は製造されています Intel Corporation、半導体技術のグローバルリーダー。もともとAlteraによって開発されたこのCPLDは、2015年にAlteraの買収に続いてIntelの製品ポートフォリオの一部になりました。それ以来、Intelはプログラム可能なソリューショングループの下でEPM7160ELC84-15を含むMAX 7000シリーズをサポートし続けています。Intelのスチュワードシップにより、デバイスは高度な製造基準、長期的な信頼性、およびドキュメントサポートから利益を得ます。現在、EPM7160ELC84-15のようなプログラム可能なロジックデバイスにおけるIntelの遺産は、世界中のレガシーシステムと専門的なアプリケーションで引き続き機能し続けています。

結論

EPM7160ELC84-15は、柔軟なプログラミング性を備えた費用対効果の高いロジック統合を求めるエンジニアとシステムデザイナー向けに調整された非常に有能なCPLDとして立っています。EEPROMベースのメモリ、高速伝播遅延、および複数の電圧レベルとの互換性により、多様な電子環境に強く適合します。Intelの製造遺産に裏打ちされ、Multivolt I/OやJTAGコンプライアンスなどの機能を備えたこのデバイスは、陳腐化にもかかわらずレガシーと専門システムでサービスを提供し続けています。EPM7160ELC84-15は、産業用自動化、組み込みアプリケーション、またはテレコムインフラストラクチャで作業しているかどうかにかかわらず、信頼できるパフォーマンスと長期的な価値を提供します。

データシートPDF

EPM7160ELC84-15データシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1. EPM7160ELC84-15と新しいCPLDまたはFPGASの違いは何ですか?

EPM7160ELC84-15は、EEPROMベースであり、外部構成メモリを必要としないため、よりシンプルまたはコストに敏感なアプリケーションに最適です。新しいCPLDまたはFPGAは、より多くのロジック容量、パフォーマンスの速度、または高度な機能を提供する場合がありますが、多くの場合、より高いコストと複雑さで提供されます。デザインがハイエンドリソースを必要としない場合、このデバイスはより効率的な選択肢です。

2.EPM7160ELC84-15をプログラムするには、どのソフトウェアが必要ですか?

Altera Max+Plus IIまたはIntel Quartus IIソフトウェアを使用して、EPM7160ELC84-15を設計、コンパイル、シミュレート、プログラムできます。これらのツールは、古いMAX 7000シリーズCPLDをサポートし、概略図とHDLベースの設計オプションの両方を提供します。

3.EPM7160ELC84-15を何回再プログラムできますか?

EPM7160ELC84-15は、EEPROMテクノロジーのおかげで最大100回再プログラムできます。これにより、プロトタイピング中および展開後であっても、長期的な柔軟性を提供する展開中であっても、更新と変更が可能になります。

4。EPM7160ELC84-15は混合電圧ロジックレベルをサポートしていますか?

はい、MultiVolt™I/Oをサポートします。つまり、5V、3.3V、または2.5Vで動作するデバイスとインターフェイスして、異なる電圧環境に適応し、混合テクノロジーシステムに統合できるようにすることができます。

5.このCPLDをプログラミングするためにUSB-Blasterを使用できますか?

はい、USB-Blaster、ByteBlasterMV、およびMasterBlasterは、JTAGを介してEPM7160ELC84-15を介してシステム内プログラミング(ISP)に接続する互換性のあるプログラミングツールです。

AD9984AKSTZ-170について知っておくべきこと

04/18/2025で公開されています

電子回路でコンデンサが行うこと

04/17/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/19/8000で公開されています 147781

-

USB-Cピンアウトと機能

04/19/2000で公開されています 112056

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/19/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/19/0400で公開されています 83811

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79624

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66995

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63119

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63057

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54097

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52207