EPM7192SQC160-15 CPLD:機能、ピンアウト、プログラミング、アプリケーション

このガイドでは、MAX 7000Sファミリーのプログラム可能なロジックチップであるEPM7192SQC160-15について説明しています。チップが何ができるか、どのように機能するか、どこで使用できるかを説明します。チップが内部にどのように構築されているか、各ピンが何をするか、それが他の部分にどのように接続するかを示します。このガイドには、このチップを使用できる場所、段階的にプログラムする方法、他の同様のチップが存在する方法、および誰が作成するかも含まれます。カタログ

EPM7192SQC160-15とは何ですか?

EPM7192SQC160-15 Max 7000SファミリーのミッドレンジCPLD(複雑なプログラム可能なロジックデバイス)であり、組み込みおよび産業システムで信頼できるデジタルロジック制御のために作られています。このチップは、192のマクロセルと約3,750のロジックゲートを提供し、中程度のロジックタスクを処理するのに十分な能力を提供します。124のI/Oピンが含まれ、5V電源で動作し、3.3Vおよび5Vロジックシステムの両方とのインターフェースをサポートするマルチボルトI/Oサポートを備えています。そのシステム内のプログラム可能なEEPROMベースのアーキテクチャにより、追加のコンポーネントや外部メモリを必要とせずに、JTAGを使用して回路に直接再プログラムできることを意味します。–15のスピードグレードでは、最大約76.9 MHzのシステムクロック周波数をサポートし、幅広いデジタルアプリケーションに高速かつ一貫したタイミングパフォーマンスを提供します。MAX 7000Sファミリーは、その堅実な性能、EEPROMメモリ、柔軟な電圧動作で知られています。

EPM7192SQC160-15をお探しですか?現在の在庫、リードタイム、価格を確認するには、お問い合わせください。

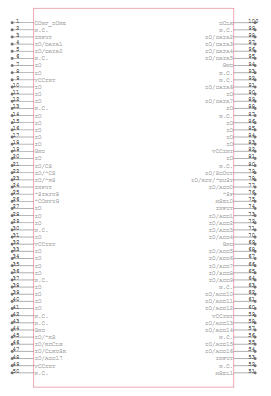

EPM7192SQC160-15 CADモデル

EPM7192SQC160-15シンボル

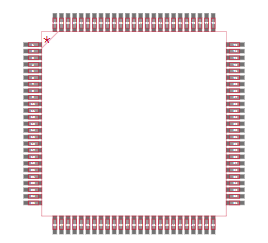

EPM7192SQC160-15フットプリント

EPM7192SQC160-15 3Dモデル

EPM7192SQC160-15機能

192マクロセル:デバイスには、コアプログラム可能な要素として機能する192のマクロセルが含まれています。これらのマクロセルは、デジタル設計で必要なさまざまな組み合わせロジック関数を実装するように構成できます。

約3,750のロジックゲート:約3,750ゲートの同等のロジック容量を提供し、埋め込みシステムの中程度の複雑さの制御ロジック、状態マシン、または接着ロジックに適しています。

JTAGを介したシステム内プログラマ性:標準のJTAGインターフェイスを使用してシステム内で直接再プログラミングできるEEPROMベースのメモリを備えており、IEEE 1149.1とIEEE 1532標準の両方をサポートしています。

最大125 MHzまでの最大周波数:内部ロジックは、125 MHzに達するクロック速度で動作し、タイミングに敏感なアプリケーションの高速処理を可能にします。

7.5 nsの伝播遅延:CHIPは、約7.5ナノ秒の伝播遅延が低く、入力から出力への迅速な信号応答を確保します。

マルチボルトI/Oで5V供給をサポートします:デバイスは5Vコア電源で実行され、マルチボルトI/Oをサポートするため、5Vと3.3Vの両方の信号レベルとの互換性が可能になり、混合電圧システムに簡単に統合できます。

プログラム可能なスルーレートとオープンドレイン出力:EMI削減の信号エッジレートを制御し、有線およびロジックまたはレベルシフトのオープンドレイン出力を選択できます。

6つのグローバル出力が信号を有効にします:これらのグローバル制御信号により、効率的な信号管理のために、複数のI/Oバンクの出力を有効または無効にすることができます。

マクロセルの構成可能なフリップフロップ:各マクロセルには、プリセット、クリア、クロックイネーブル、および個別のコントロールをサポートするフリップフロップが含まれており、シーケンシャルロジック設計の柔軟性が向上します。

低電力モード:デバイスには、マクロセルの消費電力を50%以上削減できる発電機能が含まれています。これは、エネルギー効率の高いアプリケーションに有益です。

JTAG境界スキャンテストサポート :このような128以上のマクロセルを備えたデバイスには、効率的なボードレベルの診断と検証のための完全な境界スキャンテスト機能が含まれています。

設計保護のためのセキュリティビット:プログラム可能なセキュリティビットにより、内部設計を読み取ったりコピーしたりすることができず、知的財産を保護します。

PCI互換I/O:I/O構造は、PCIの電気要件を満たすように設計されており、PCIベースのシステムとの直接的なインターフェースを可能にします。

動作温度範囲0°C〜70°C:標準の商業グレードの温度範囲により、このデバイスはほとんどの屋内および制御環境アプリケーションに適しています。

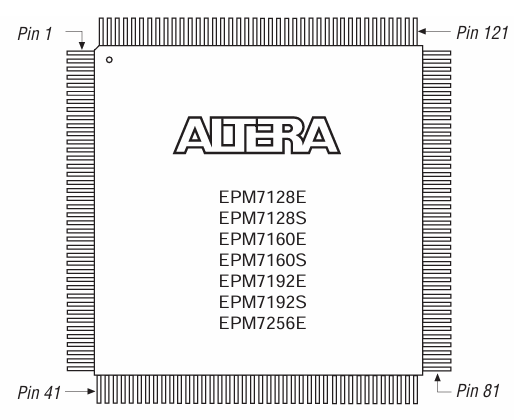

EPM7192SQC160-15ピンアウト図

この図は、EPM7192SQCC160-15および同様のAltera Max 7000Sデバイスのピンレイアウトを示しています。チップには、正方形のQFPパッケージにある4つの側面すべてに配置された160個のピンがあります。ピン1は左上のコーナーから始まり、数字はチップの周りで反時計回りに進みます。両側には40個のピンがあります。左上のマークピン1の小さなドットは、適切な配置に役立ちます。中央のチップ名は、同じファミリの他のモデルと互換性があることを示しています。このレイアウトは多くのI/O接続を提供し、複雑なロジック設計に役立ちます。

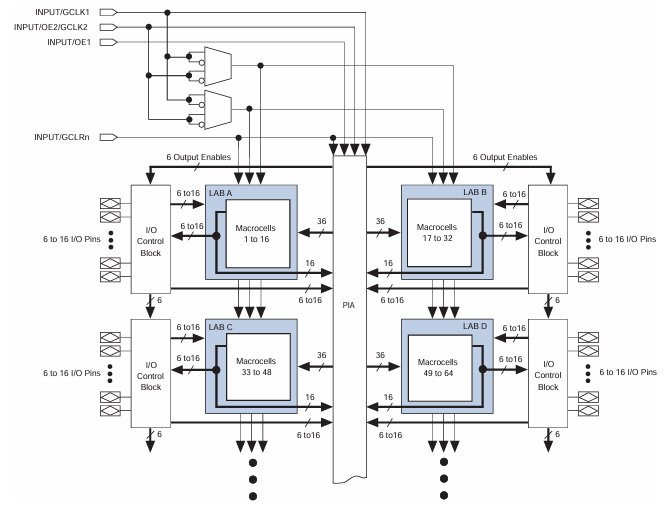

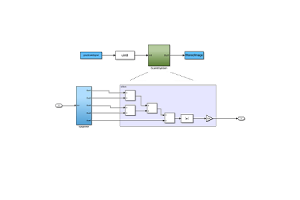

最大7000Sブロック図

このブロック図は、EPM7192SQC160-15を含む最大7000S CPLDの内部構造を示しています。チップは、ロジックアレイブロック(ラボAからD)と呼ばれる4つのメインセクションに分割されます。各ラボには16のマクロセルがあり、デジタルサーキットの構築に使用される小さなロジックユニットです。一緒に、これらのラボは複雑なロジック操作を処理します。

中央には、すべてのラボを接続し、データを共有できるプログラム可能な相互接続配列(PIA)があります。各ラボは、36チャネルを介して信号を送信および受信し、ロジックブロック間の柔軟なルーティングを提供します。エッジの周りには、6に16 I/Oピンを各ラボにリンクするI/Oコントロールブロックがあり、デバイスがシステムの他の部分に接続できるようにします。

上部には、クロックや出力などのグローバル制御信号が表示されます。これらの信号は、チップ内のデータがどのように移動するか、出力がアクティブな場合に管理するのに役立ちます。全体として、この図は、EPM7192SQC160-15がロジックと接続を整理してカスタムデジタルデザインをサポートする方法を示しています。

EPM7192SQC160-15仕様

|

タイプ |

パラメーター |

|

メーカー |

アルター |

|

シリーズ |

MAX®7000S |

|

パッケージング |

トレイ |

|

パーツステータス |

廃止 |

|

プログラム可能なタイプ |

プログラム可能なシステムで |

|

遅延時間TPD(1)最大 |

15 ns |

|

電圧供給 - 内部 |

4.75V〜5.25V |

|

ロジック要素/ブロックの数 |

12 |

|

マクロセルの数 |

192 |

|

ゲートの数 |

3750 |

|

I/Oの数 |

124 |

|

動作温度 |

0°C〜70°C(TA) |

|

取り付けタイプ |

表面マウント |

|

パッケージ /ケース |

160-BQFP |

|

サプライヤーデバイスパッケージ |

160-PQFP(28x28) |

|

基本製品番号 |

EPM7192 |

EPM7192SQC160-15アプリケーション

組み込みシステム接着ロジック

EPM7192SQC160-15は、組み込みシステムにさまざまなデジタルデバイスを埋めるのに最適です。これは、個別の論理を必要とせずにアドレスデコード、バス制御、およびタイミング調整を処理することにより、マイクロコントローラー、メモリチップ、およびI/Oデバイス間の通信を管理するために使用できます。

状態マシンと制御ロジック

192のマクロセルを備えたこのチップは、カスタムステートマシンと制御ロジックを実装するのに適しています。これは、自動化タスク、モーターコントローラー、および信頼性が高く再現可能な状態遷移を必要とするタイミングベースの制御システムで一般的に使用されています。

通信プロトコルインターフェイス

このCPLDは、UART、SPI、I²C、カスタムシリアル形式などの通信プロトコルを作成または翻訳するようにプログラムできます。ハードウェアを変更せずに簡単な構成と変更を可能にするため、通信のインターフェースに役立ちます。

デジタル信号の前処理

高速のロジック速度と低伝播遅延のおかげで、信号がメインプロセッサまたはDSPチップに到達する前に、フィルタリング、多重化、またはエッジ検出などの単純な信号処理タスクを処理できます。

インターフェイス変換とレベルシフト

マルチボルトI/O機能は、3.3Vと5Vの両方の信号をサポートします。これにより、異なる電圧レベルで動作するコンポーネントを含む設計に適しており、安全で効率的な電圧翻訳が可能になります。

迅速なプロトタイピングとシステム内の更新

このチップは、頻繁にロジック更新を必要とする可能性のあるシステムで使用できます。EEPROMベースの構造とJTAGプログラミングインターフェイスにより、ボードが組み立てられた後でもロジックを再プログラムできます。

ボードレベルのテストと診断

JTAGを介して境界スキャンサポートを使用すると、プローブを必要とせずにPCBのチップ間の接続をテストします。これは、はんだ付けやルーティングの問題を検出するための製造およびフィールド診断中に役立ちます。

EPM7192SQC160-15同様の部品

• EPM7192EQC160-20 (アルテラ)

このデバイスは同じMax 7000シリーズのもので、同じロジックリソース、192のマクロセル、160ピンPQFPパッケージの124 I/Oピンを提供しています。–20のスピードグレードが遅いため、伝播遅延(〜20 ns)が長いことを意味しますが、非時代のデザインのニーズを満たしています。これは、論理密度が重要なアプリケーションに適した代替品ですが、超高速タイミングは優先事項ではなく、機能的な同等性が必要なコストに敏感なプロジェクトに最適です。

• EPM7192SQI160-10N (アルテラ)

この部分は、EPM7192SQC160-15でも論理互換性があり、同じ数のマクロセルとI/OSを提供します。ただし、タイミングが改善された(10 ns伝播遅延)により速い操作をサポートする–10速度グレードを使用します。また、–40°Cから +85°Cの拡張温度範囲をサポートしているため、産業用または屋外アプリケーションの優れた代替品となっています。これにより、高速と環境の回復力が必要な場合に理想的になります。

• EPM7192SQC160-7 (インテル)

EPM7192SQC160-15の直接スピードアップバリアントとして、–7バージョンは家族で最速のパフォーマンスを提供し、伝播遅延は7.5 nsに低下します。同じピン構成、電源仕様、ロジック密度を維持し、ボードレイアウトや電圧要件を変更せずに、より良い速度を求めている人にドロップイン交換を提供します。これにより、同じデザインフットプリント内にとどまる間、より速い信号応答が必要なタイミングクリティカルなデザインに最適な選択肢になります。

EPM7192SQC160-15プログラミング手順

1. ISPモードを入力します

最初のステップは、デバイスをISP(システム内プログラミング)モードにシフトすることです。これは、JTAGインターフェイスを介して行われます。ISPモードになったら、デバイス上のすべてのI/Oピンは、プログラミング中の意図しないロジック干渉を防ぐために、安全な3つの状態モードに配置されます。この初期化は通常、約1ミリ秒かかります。

2.デバイスIDを確認します

独自のシリコンIDがデバイスに埋め込まれており、プログラミングが開始される前に正しいモデルであることを確認します。システムは読み取り命令にシフトし、TDO(テストデータアウト)行を介してIDを取得します。このチェックにより、プログラミングツールが適切なCPLDに接続されていることが保証され、別の部分を上書きするような間違いを回避します。

3.バルク消去

バルク消去は、CPLDのEEPROMメモリに以前に保存されたすべてのデータをクリアします。これにより、新しい構成を受信するためにチップが準備されます。消去コマンドは、通常約100ミリ秒続くパルスを開始し、すべてのプログラム可能なセルがリセットされるようにします。

4.プログラムEEPROM

新しい構成データは、JTAGポートを介してアドレスとデータビットをシフトすることにより、デバイスにロードされます。各メモリセルは1つずつ記載されており、成功した書き込みサイクルのたびにプログラミングパルスが適用されます。このプロセスは、CPLDが電源を入れたときに使用するロジック構造を定義します。

5. EEPROMを確認します

プログラミング後、デバイスは検証ステップを実行します。これには、プログラムされた各メモリの位置を読み返し、意図したデータと出力値を比較することが含まれます。検証が失敗した場合、プロセスを繰り返す必要があります。このステップにより、構成が正常に記述されたことが保証されます。

6. ISPモードを終了します

確認が完了すると、ISPモードを終了するために最終コマンドが発行されます。デバイスはI/Oピンを再アクティブ化し、通常の動作を再開します。この遷移には約1ミリ秒かかり、システム内プログラミングサイクルが完了します。

EPM7192SQC160-15パッケージングの寸法

• 体の大きさ:28mm×28mm

• パッケージの高さ:3.4mm

• ピンピッチ:0.65mm

EPM7192SQC160-15メーカー

EPM7192SQC160-15は元々製造されていました Altera Corporation、高度なプログラム可能なロジックデバイスで知られる会社。2015年、Alteraが買収されました Intel Corporation、そしてこのデバイスは、Max 7000S CPLDファミリーの下でIntelのプログラム可能なソリューショングループの一部になりました。Intelはレガシーアルテラ製品をサポートし続けていますが、EPM7192SQC160-15は現在、ほとんどの公式カタログで時代遅れに分類されています。その中止されたステータスにもかかわらず、インテルの信頼性に対する歴史的評判と、高性能ロジックソリューションにおけるアルテラの遺産により、二次ディストリビューターを通じて継続的な需要と可用性が保証されます。

結論

EPM7192SQC160-15は、多くの電子システムでデジタル制御タスクを処理するための便利で柔軟なチップです。カスタムステートマシンの構築、信号の取り扱い、さまざまなデバイスの接続などのジョブに十分なロジックパワーを提供します。異なる電圧レベルをサポートし、速い速度で動作し、JTAGを介して簡単に更新できます。その内部設計により、滑らかな信号の流れと簡単なロジックの変更が可能になります。現在は中止されていますが、古いプロジェクトや進行中のプロジェクトにとってはまだ素晴らしい選択肢であり、より速いまたはより広い温度サポートを提供する同様のチップに置き換えることができます。

データシートPDF

EPM7192SQC160-15データシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1. EPM7192SQC160-15を回路基板から削除せずにプログラムできますか?

はい、CHIPはJTAGインターフェイスを介してシステム内プログラミング(ISP)をサポートしているため、PCBではんだ付けされている間に直接プログラムまたは再プログラムすることができます。

2.EPM7192SQC160-15にどのようなプログラミングソフトウェアを使用すればよいですか?

AlteraのQuartus IIソフトウェア(古いバージョン)を使用して、ロジックデザインを作成し、コードをコンパイルし、JTAGベースのプログラミングプロセスを管理できます。Quartus IIは、EPM7192SQC160-15などの最大7000Sデバイスをサポートしています。

3。EPM7192SQC160-15は、動作に外部メモリを必要としますか?

いいえ、内部EEPROMベースの構成メモリがあります。すべてのロジック構成はチップ内に保存されるため、ロジック状態またはブートシーケンスを保存するために外部メモリは必要ありません。

4. EPM7192SQC160-15が産業用に適している理由は何ですか?

その堅牢な5V操作、マルチボルトI/O互換性、高速論理処理、およびEEPROMベースの非揮発性メモリにより、安定した耐久性のあるデジタルロジック機能を必要とする産業システムに対して信頼性が高くなります。

5.EPM7192SQC160-15は混合電圧システムをどのように処理しますか?

マルチボルトI/Oサポートのおかげで、このデバイスは3.3Vおよび5Vロジックレベルの両方とインターフェースでき、混合シグナルシステムと最新の低電圧コンポーネントとのインターフェースに最適です。

プロジェクトにEPF10K100EFC484-3を選択する理由

06/13/2025で公開されています

SPSTスイッチとは何ですか?また、どのように機能しますか?

06/12/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/17/8000で公開されています 147710

-

USB-Cピンアウトと機能

04/17/2000で公開されています 111648

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/17/1600で公開されています 111313

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/17/0400で公開されています 83571

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79208

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66738

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 62923

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 62784

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54018

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 51932