GC5330IZEVデジタル信号プロセッサ:機能、アプリケーション、代替、仕様

このガイドは、ワイヤレスシステムがより適切に機能するのに役立つスマートデジタルチップであるGC5330Izevに関するすべてです。セルタワー、ワイヤレスリピーター、テスト機器などで使用されます。GC5330izevは、多くのワイヤレス信号を処理し、速度を改善し、ノイズを減らし、信号をより明確にするのに役立ちます。このガイドでは、このチップが何をするか、どのように機能するか、どこで使用されているかを学びます。カタログ

GC5330izevの概要

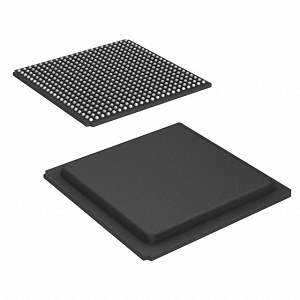

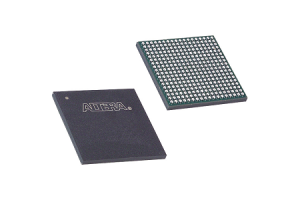

gc5330izev 高度なワイヤレス通信システム専用に設計された、洗練されたワイドバンド送信 - 受信デジタル信号プロセッサ(DSP)です。このDSPは、CDMA、GSM、TD-SCDMA、W-CDMA、WIMAXなどの多様な標準範囲をサポートしているため、さまざまな通信インフラストラクチャに非常に汎用性があります。表面マウントテクノロジーアプリケーションに適した484ボールグリッドアレイ(BGA)パッケージを備えており、最新の電子アセンブリへのシームレスな統合を確保しています。より広範なGC5330ファミリの一部であるGC5330Izevは、広帯域送信受信運用のパフォーマンスと効率を最適化することを目的とした兄弟と共通のコアアーキテクチャを共有しています。

システム用の信頼できるDSPをロックすることを検討している場合は、GC5330izevにバルクオーダーを配置することを考える絶好の機会です。

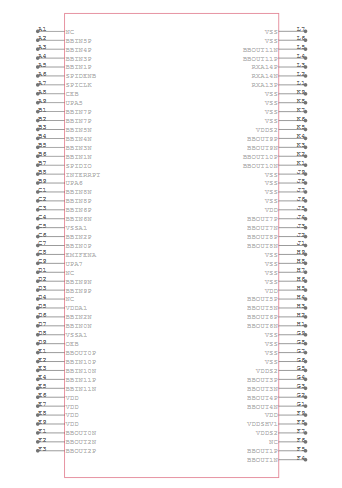

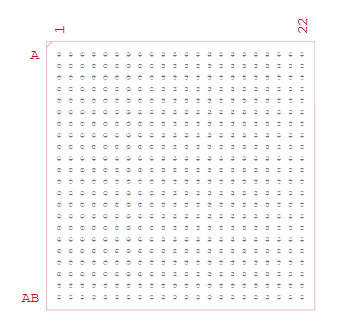

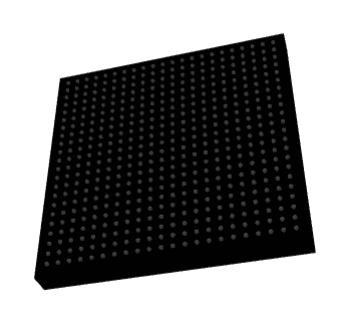

GC5330izev CADモデル

GC5330izevシンボル

GC5330IZEVフットプリント

GC5330IZEV 3Dモデル

GC5330izev機能

• 統合された送信およびソリューションの場合はデジタルを受け取ります:DSPには、統合されたデジタルアップコンバーター(DUC)とデジタルダウンコンバーター(DDC)機能が含まれます。この統合により、複数の機能を1つのコンパクトソリューションに組み合わせることにより、信号処理チェーンが簡素化され、システムの複雑さとサイズが削減されます。

• 複数のチャネルサポート:GC5330izevは、最大4つの送信(TX)および8つの受信(RX)チャネルをサポートします。この機能により、複雑なマルチアンテナシステムの処理が可能になります。これは、高データスループットと強化された信号の整合性を必要とする最新のワイヤレス通信技術に最適です。

• パス機能を送信します:GC5330izevの送信パスの主要な機能には、CREST因子削減(CFR)、デジタルプレッシ留置(DPD)、および送信イコライゼーションが含まれます。これらの機能は、信号の品質と直線性を改善するために必要であり、これにより、コミュニケーションシステムの全体的な効率とパフォーマンスが向上します。

• 同期機能:デバイスには、2つのLVD入力同期(SYNCAおよびSYNCB)と1つのLVDS出力同期が装備されています。これらの同期機能は、データ送信の整合性と一貫性を維持するために、システム内の複数のデバイスにわたって正確なタイミングの調整を保証します。

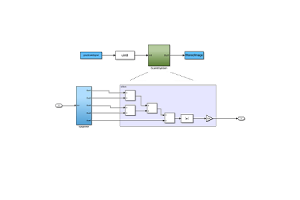

gc5330izevブロック図

GC5330/GC5337のブロック図は、基地局システム向けに設計された高性能デジタル送信ソリューションを示しています。それはaで始まります ベースバンドインターフェイス、デジタルベースバンドデータをチップに運ぶ1.8Vで最大24のLVD差差ペアを受信します。このインターフェイスには、チャネルごとの電源メーターが含まれています AGC (自動ゲイン制御) 最適な信号レベルを確保します。 デジタルダウン/アップコンバーター(DDUC)ブロック 送信(TX)または受信(RX)のいずれかで構成可能で、最大12チャネルをサポートします。FIR、Farrow、CICなどの複数のフィルタリング段階を介してベースバンド信号を処理して、サンプルレートを調整し、補間またはデシメーションを適用します。オプション 数値制御オシレーター(NCO) 周波数変換にも含まれています。フィルター処理されて条件付けたら、信号はTXパスに入り、CFR(CREST因子の減少)とDPD(デジタルプレディストリスターション)ブロックによってさらに補間されます。これらのコンポーネントは、信号の動的範囲を最適化し、効率的な伝送のために線形化します。ET(エンベロープ追跡)およびBUC(ブロックアップコンバーター)要素は、高周波変調の信号を準備します。IF NCOステージは、TX形式とDACインターフェイスに送信される前に、信号を中間周波数にシフトします。

受信側では、システムは60のLVDSラインを介して高速ADCデータをキャプチャします。データは、DCオフセットキャンセル、FE-AGC、スイッチ、およびNCOブロックの場合に処理されます。次に、最終的なキャプチャと電力測定の前に、R2CとBDCに進み、イコライゼーションを通過し、I/Qの不均衡補正を通過します。このプロセスは、柔軟な帯域幅とデシメーションレートをサポートします。図の下部に、いくつかの制御および同期インターフェイスが示されています。これらには、コマンドとデータ入力用のマイクロプロセッサインターフェイス、テストとデバッグ用のJTAG、および構成用SPIが含まれます。高速クロックと同期信号は、入力、処理、および出力ブロック間の正確なタイミングを確保します。全体として、GC5330/GC5337アーキテクチャは、さまざまなワイヤレス標準の柔軟な構成可能性を備えた高効率デジタルトランスミッションに最適化されています。

GC5330izev仕様

|

タイプ |

パラメーター |

|

メーカー |

テキサスの楽器 |

|

パッケージング |

バルク |

|

パーツステータス |

廃止 |

|

関数 |

デジタル信号プロセッサ |

|

RFタイプ |

CDMA、GSM、TD-SCDMA、W-CDMA、WIMAX |

|

取り付けタイプ |

表面マウント |

|

パッケージ /ケース |

484-BGA |

|

サプライヤーデバイスパッケージ |

484-BGA |

|

基本製品番号 |

GC5330 |

GC5330izevアプリケーション

ワイヤレス通信システム

GC5330izevは、CDMA、GSM、TD-SCDMA、W-CDMA、WIMAXなどの高度なワイヤレスプロトコルを処理するように設計されています。これにより、最新のベースステーションやワイヤレスインフラストラクチャで使用するのに理想的なDSPになります。統合されたデジタルアップコンバージョンとダウンコンバージョン機能は、複数のチャネルサポートとともに、ワイドバンドRF信号処理を効率的に管理できるようにします。このデバイスは、必要な外部コンポーネントの数を減らし、優れた信号の完全性を提供することにより、ワイヤレス通信システムのパフォーマンスを向上させます。

ワイヤレスリピーター

ワイヤレスリピーターアプリケーションでは、GC5330izevは受信チェーンと送信チェーンの間のブリッジとして機能します。デジタルフィルタリング、着信信号のダウンコンバージョン、および発信信号のアップコンバージョンを提供します。これにより、リピーターは歪みのない長い距離で通信信号を中継することができます。Crest Factorの削減やデジタルの耐久性などの機能を含めることで、増幅されたパスの伝送品質を維持するのにも非常に適しています。

テストおよび測定機器

GC5330izevは、テストおよび測定機器において価値があります。そのワイドバンド処理機能と柔軟なチャネル処理により、さまざまなワイヤレスプロトコル全体でシグナルをシミュレート、処理、分析できます。高い同期精度と高度な信号条件付け機能は、ラボおよびフィールドテスト環境での信頼性の高い再現可能な測定を確保するのに役立ちます。

ポイントツーポイントラジオ

GC5330izevは、ポイントツーポイントマイクロ波およびミリ波波の無線リンクで使用するのに適しています。このようなシステムでは、高いデータレートの送信と受信には、広い帯域幅と緊密な同期を処理できるDSPが必要です。このデバイスは、効率的なデジタル処理でこれらのニーズをサポートし、固定ワイヤレスアクセス、バックホールネットワーク、または専門化された産業リンクで信頼できる通信を可能にします。

gc5330izev類似部品

GC5330izevの利点

強化されたパワー増幅器の効率

GC5330izevは、CREST因子の還元(CFR)とデジタルの予防(DPD)を組み込むことにより、システム全体の効率の改善を提供します。これらのテクノロジーは、RF信号のピーク対平均比(PAR)を減らし、パワーアンプの正しい非線形性を減らすために連携します。その結果、アンプはより効率的に動作し、消費電力と熱生成を減らします。これにより、システムオペレーターのコスト削減につながり、RFコンポーネントの運用寿命が延長されます。

柔軟なシステム統合

2×2、4×4、さらには4×8などのさまざまなMIMO構成のサポートと、GSM、CDMA、TD-SCDMA、W-CDMA、WIMAXなどの複数のワイヤレス標準との互換性のおかげで、GC5330izevは非常に用途が広いです。さまざまな通信インフラストラクチャタイプで単一のプラットフォームを使用して、開発の複雑さ、市場までの時間を減らし、さまざまなネットワークの複数のDSPソリューションを管理する必要があります。

コンポーネントのカウントとコストの削減

Digital Uponversion、DownConversion、および等化を単一のデバイスに送信するなどの複数の処理機能を統合することにより、GC5330Izevは外部サポートコンポーネントの必要性を最小限に抑えます。これにより、PCBレイアウトが簡素化されるだけでなく、材料請求書(BOM)コストとシステムフットプリントも削減されます。最終結果は、製造と保守が簡単な、よりコンパクトで費用対効果の高いデザインです。

信号の品質と信頼性が向上しました

CFR、DPD、送信等化などの上級信号処理が組み込まれているため、GC5330Izevは信号の明確さを強化し、隣接チャネルの漏れを減らします。これにより、より堅牢で干渉耐性のある通信チャネルが生じ、密なRF環境や高データレートのシナリオでも、ユーザーが一貫した高品質の伝送を受け取るようにします。

GC5330izevプログラミング手順

1.インターフェイスの選択:GC5330izevのプログラミングの最初のステップでは、適切な通信インターフェイスを選択することが含まれます。このデバイスは、マイクロプロセッサユニット(MPU)インターフェイスとシリアル周辺インターフェイス(SPI)の両方をサポートします。選択は、システムのアーキテクチャとデータ制御要件に依存します。SPIインターフェイスは、Emifena(外部メモリインターフェイスを有効にする)ピンがロジック低く設定されている場合にのみアクティブになります。通信を開始する前に、正しいハードウェア構成が整っていることを確認する必要があります。この決定は、コントロールコマンド、構成データ、およびステータス情報がホストコントローラーとGC5330の間で交換される方法を決定します。

2.クロック構成:インターフェイスが確立されたら、次のステップはクロック信号を構成することです。GC5330izevは、デジタル歪み前クロック(DPDCLK)とベースバンドクロック(BBCLK)の2つのメインクロックを使用して動作します。これらのクロックは、内部データ処理パイプラインを駆動します。DPDCLKは最大310 MHzの周波数をサポートし、BBCLKは最大290 MHzをサポートします。どちらも、意図したワイヤレス通信標準の帯域幅とタイミングの要件を満たすように正確に構成する必要があります。これらのクロックドメイン間の適切な同期により、フィルタリング、補間、機能の混合などの信号処理段階が確実に、および仕様内で確実になります。

3.同期:同期は、GC5330izev内のさまざまなモジュールにわたる時間並列操作に重要です。CHIPは、入力同期信号SyncaとSyncb、および出力同期信号同期を提供します。これらの信号は、パワーメーター、信号キャプチャ、DPDの更新などの内部イベントを合わせるために使用されます。マルチチップまたはマルチチャネルシステムでは、外部ハードウェアまたはベースバンドプロセッサが同期パルスを調整して、一貫した処理ウィンドウを確保する必要があります。同期制御レジスタをプログラミングすることにより、同期トリガーが発生する方法と時期をカスタマイズし、動的システム条件下でも安定した動作を確保できます。

4.データのフォーマット :GC5330izevは、送信パスと受信パスの両方の柔軟なデータフォーマットオプションを提供します。送信用のベースバンド入力フォーマッタと、受信用のベースバンド出力フォーマッタを構成する必要があります。これには、シリアル、バイトパラレル、またはナブルパラレルモードなどの適切なデータ幅と形式を選択することが含まれます。正しいデータフォーマットにより、ベースバンドプロセッサまたはFPGA処理デジタルI/Qストリームとの互換性が保証されます。プログラム可能なフレーミングオプションでは、複雑なフレーミング構造を使用したり、動的バースト送信を使用したりするシステムのカスタマイズされたアライメントマーカーとデータカプセル化を可能にします。

5. DUCおよびDDC構成:GC5330izevの主要な機能は、デジタルアップコンバージョン(DUC)とダウンコンバージョン(DDC)機能です。これらのブロックは、信号補間、デシメーション、フィルタリング、および周波数変換を管理するように構成されています。送信側では、DUCはサンプルレートを増加させ、信号を目的の周波数帯域にシフトし、RF変換に対応します。受信側では、DDCはサンプルレートを下げ、望ましくない周波数コンポーネントをフィルタリングします。適切なDUCおよびDDC設定は、信号の忠実度を最適化し、エイリアシングを削減し、効率的な帯域幅の使用を確保するのに適しています。構成パラメーターには、補間/デシメーションレート、フィルター係数、ミキサー設定が含まれます。

6.制御を獲得します:GC5330izevの自動ゲインコントロール(AGC)は、フロントエンドAGC(FEAGC)とバックエンドAGC(BEAGC)の2つの重要な領域に分割されます。これらのブロックは、シグナルが処理チェーンを通過するため、最適な信号レベルを維持するのに役立ちます。FEAGCは主に着信信号レベルを扱い、ゲインを調整して飽和またはクリッピングを防ぎます。BEAGCは、処理された信号に焦点を当て、その後のデジタル操作の予想される動的範囲内に留まるようにします。AGCしきい値、攻撃/減衰率をプログラムし、フェード、干渉、信号電力の変化などのさまざまな信号条件を処理する手順を獲得する必要があります。

7.電源メーターとアラームのセットアップ:GC5330izevには、信号レベルの監視が可能なプログラム可能な電力計量ユニットが含まれています。これらのメーターは、発電、滴、または帯域外の排出量などの異常を検出するのに役立ちます。プログラマブルアラームは、プリセットのしきい値に基づいてトリガーするように構成でき、ゲイン調整やエラーシグナル伝達などの保護または修正アクションを可能にします。電源ウィンドウサイズ、しきい値レベル、フィルター設定を設定して、メーターブロックを構成する必要があります。この機能は、規制のコンプライアンスと運用上の安全性を必要とするベースステーションなどの高い信頼性を必要とするシステムで重要です。

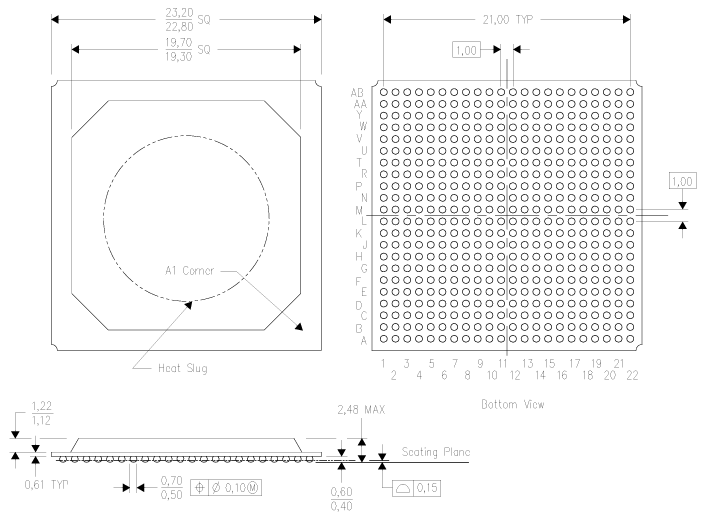

GC5330izevパッケージングの寸法

パッケージの寸法

|

パラメーター |

寸法(mm) |

|

ボディサイズ(全体) |

22.80 - 23.20 |

|

基板サイズ(内側の正方形) |

19.30 - 19.70 |

|

ボールピッチ(典型) |

1 |

|

ボールの数 |

22×AB(グリッドアレイ) |

|

パッケージの高さ(ボディ) |

1.12 - 1.22 |

|

最大パッケージの高さ(全体) |

2.48 |

|

ボールの直径 |

0.50 - 0.70 |

|

座席機の上のボールの高さ |

0.40 - 0.60 |

|

ボールの直径の耐性 |

±0.10 |

|

ボールスタンドオフ(座席機) |

0.15 |

パッケージの概要

GC5330Izevメーカー

GC5330izevは製造されています テキサスの楽器、アナログおよび埋め込まれた加工半導体の設計と生産における世界的に有名なリーダー。テキサス州ダラスに本社を置くテキサス州インスツルメンツ(TI)は、電子機器業界の革新と信頼性について長年の評判を持っており、自動車、産業、通信、家電などの多様なセクターにサービスを提供しています。TIは、高性能統合回路の堅牢なポートフォリオで知られており、GC5330Izevは、複雑なデジタルラジオソリューションの提供における同社の専門知識を例示しています。テキサスインスツルメンツは、品質、スケーラビリティ、および新たな通信基準のサポートに焦点を当てているため、GC5330Izevなどのコンポーネントが最新のRFおよびベースバンド処理アプリケーションの要件を満たすことを保証します。

結論

GC5330izevは、次世代のワイヤレスインフラストラクチャの厳しい要求を満たすために設計された高性能DSPソリューションとして際立っています。柔軟なチャネルサポート、統合処理ブロック、および堅牢な同期により、システムの複雑さを減らし、電力増幅器の効率を改善し、信号の忠実度を高めるのに理想的です。Texas Instrumentsの信頼性と革新に対する評判に裏付けられたGC5330Izevは、最小限のコンポーネントオーバーヘッドを備えたスケーラブルで効率的なRFシステムを構築することを目指しており、頼りになる選択肢です。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1。GC5330IZEVは、カスタムFPGAベースのシステムと互換性がありますか?

はい、GC5330izevは、カスタムFPGAベースのシステムと非常に互換性があります。構成可能なデジタルインターフェイスとデータフォーマットオプションにより、プログラム可能なロジックプラットフォームと簡単に統合できます。LVDSデータリンク、SPI、またはマイクロプロセッサインターフェイスを使用して、FPGAとDSPチップ間で通信して、ベースステーションやテスト機器などのアプリケーションでシームレスな信号処理を確保できます。

2。GC5330Izevは、離散DSPセットアップと比較して信号の品質をどのように改善しますか?

複数の個別のDSPコンポーネントに依存する従来のセットアップとは異なり、GC5330Izevは、Crest Factor削減(CFR)、デジタルプレディスターション(DPD)、高度なフィルタリングなどの主要な機能を統合します。この統合により、信号の整合性、低下、およびより良い同期に対するより厳しい制御が保証され、直接誤差ベクトルの大きさ(EVM)が改善され、隣接するチャネル干渉が減少します。

3。GC5330IZEVは、5Gサブ6 GHzシステムで使用できますか?

GC5330izevは主に3Gおよび4Gワイヤレス標準用に設計されていましたが、超低レイテンシまたは大規模なMIMOスケーラビリティを必要としないサブ6 GHz 5Gシステムの強力な処理ブロックとして機能します。帯域幅の高いサポートと複数のTX/RXチャネルは、ワイドバンド信号を処理し、移行可能な5G展開での固定ワイヤレスアクセスまたはバックホールをサポートするのに役立ちます。

4. Multi-BandまたはCarrier Aggregation SystemsにGC5330Izevを使用できますか?

はい、GC5330izevは、マルチチャネルデジタル処理アーキテクチャを通じてマルチバンドシステムをサポートできます。同時に、最大4つのTXと8つのRXチャネルを処理できます。これにより、特にRFフロントエンドの場合はデジタルを必要とするシナリオで、周波数帯域全体でキャリア集約を実装できます。最適なパフォーマンスには、注意深いクロッキングと同期設定が必要です。

5.ソフトウェア定義ラジオ(SDR)を備えたシステムでGC5330izevを使用できますか?

はい。GC5330izevは、SDRアーキテクチャ、特に集中的なベースバンド処理に専用のハードウェアDSPが必要なSDRアーキテクチャと互換性があります。リアルタイムのデジタル変換とチャネル化機能により、SDR環境の一般的なプロセッサからのコンピューティングが高いタスクをオフロードすることができます。

EPF8820AQC208-4 FPGA:機能、仕様、プログラミング、およびデータシート

04/1/2025で公開されています

EP1C4F324C7N FPGA:データシート、機能、プログラミング、仕様

04/1/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/18/8000で公開されています 147776

-

USB-Cピンアウトと機能

04/18/2000で公開されています 112022

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/18/1600で公開されています 111351

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/18/0400で公開されています 83777

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79577

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66964

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63104

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63041

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54097

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52190