HDL:デジタル回路設計のイノベーションのロックを解除します

このガイドでは、抽象的なデザインを実際の製造可能な回路に変えるための重要なツール、ハードウェアの説明言語(HDL)を探ります。それらの進化、ASICおよびFPGA設計のアプリケーション、および最新の電子機器への影響をカバーしています。例と専門家の洞察を通して、このガイドは、HDLの理解を深め、理論と実践的なスキルの両方を強化することを目的としています。HDLSがアイデアと物理的デバイスのギャップをどのように埋めるかを発見し、テクノロジーの革新を促進します。カタログ

デジタル設計におけるHDLの役割

ハードウェア説明言語(HDL)は、複雑な回路をモデル化する構造化された方法を提供することにより、デジタルシステムの設計に役割を果たします。大規模なシステムを、電子設計自動化(EDA)ツールを使用してテストおよび検証された、より小さな管理可能なモジュールに分解できます。検証されると、これらのモジュールはゲートレベルのネットリストに合成され、ASICまたはFPGAの配置とルーティングを介して物理サーキットに変換されます。Silicon Valleyなどの業界で広く使用されているHDLは、設計の制約のバランスをクリエイティブソリューションと支援することにより、イノベーションを推進し、デジタルテクノロジーの進歩に重要な要素となっています。

HDLの歴史的発展

ハードウェア説明言語(HDL)の開発は、1980年代後半までに、断片化されたニッチなツールからVHDLやVerilogなどの標準化された業界全体のソリューションに進化する数十年に及びます。これらの標準化されたHDLS統合設計慣行とコラボレーションの改善。テクノロジーが進歩するにつれて、HDLSはより複雑なシステムをサポートするために拡張され、SystemCやSuperlogなどの新しい言語をハードウェアとソフトウェア設計を埋めました。HDLSは、コミュニケーションの改善、エラーの削減、設計プロセスの合理化において価値を示しています。HDLSの進行中の進化は、現代のテクノロジー開発に対するデジタル設計の変化する需要を満たすために継続的なイノベーションの必要性を反映しています。

目的

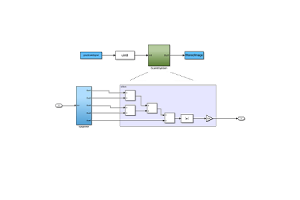

1970年代以来ムーアの法律によって駆動される統合サーキットがより複雑になったため、設計方法論は個々のコンポーネントに焦点を当てることから、システムレベルのデータフローとタイミングの管理に移行しました。このシフトは、登録転送レベル(RTL)抽象化の採用につながりました。これにより、製造の詳細に早期に対処する必要なく、ロジック機能とタイミングに集中できます。ハードウェア説明言語(HDL)でサポートされているRTL抽象化は、パフォーマンス、パワー、スケーラビリティのバランスをとることにより、設計プロセスを合理化します。設計サイクルを削減し、コラボレーションを強化し、潜在的な問題を予測し、費用のかかる改訂を防ぎます。より高い抽象化レベルに焦点を当てることにより、急速に進化する技術環境におけるより大きな効率、適応性、革新のロックを解除します。

構造特性

ハードウェア説明言語(HDL)は、回路システムの構造、動作、およびタイミングを定義するテキストフレームワークとして機能します。それらは並列プログラミング言語のように機能しますが、タイミングとハードウェアの接続の管理に特に調整されています。HDLSは、さまざまな抽象化レベル、構造、行動、およびレジスタ移動にわたって動作し、さまざまな視点から回路設計にアプローチします。構造レベルでは、HDLSは概略図に似たコンポーネントと接続を詳細にします。動作レベルは、回路が何をすべきかに焦点を当て、レジスタ転送レベル(RTL)はレジスタ間のデータフローと操作、機能性、ハードウェアの詳細のバランスをとることを説明します。HDLSはロジック合成もサポートし、高レベルの設計をゲートレベルの回路に変換し、ハードウェアの展開前に機能をテストするシミュレーションをサポートします。従来のプログラミング言語とは異なり、HDLは主にハードウェアの動作をキャプチャするツールをモデリングし、正確で革新的なサーキット設計に重要にしています。

HDLのデータフローの調査

制御フローを優先する従来のプログラミング言語とは異なり、HDLはハードウェア開発とシミュレーションのためのサーキットのタイミングのモデリングに焦点を当てています。ハードウェアの時間的動作をキャプチャするこのユニークな機能は、C ++などの言語とは別にHDLを設定します。SystemVerilogなどの最新のHDLは、プログラミングのパラダイムをますますブレンドしており、オブジェクト指向の概念を組み込んで、複雑なシステム設計のモジュール性と維持可能性を改善しています。HDLSは、ロジック合成にも役割を果たし、高レベルの説明をゲートレベルの実装に変換し、抽象設計が物理的制約と一致するようにします。さらに、シミュレーションと検証には、シミュレーションと検証に、生産前に回路の動作を厳密にテストするために使用されます。HDLSが進化し続けるにつれて、ハードウェアの複雑さの増加に対処するために、より多くのソフトウェアのような機能を採用し、ハードウェアの精度と友好的な抽象化のギャップを埋める可能性があります。

HDLを使用した統合回路設計の強化

ハードウェアの説明言語(HDLS)は、抽象的なアイデアを実用的な実行可能な計画に変換することにより、統合サーキットを設計する複雑なプロセスを合理化します。多くの場合、多くの場合、フローチャートと状態図を使用して回路ロジックをマップしてから、建設用の青写真を作成するのと同じように、正確なHDLコードに変換します。回路要件を順守している間、他の人は、アルゴリズムとスクリプトを組み込んで繰り返しタスクを簡素化することにより、独自のスタイルをコーディングにもたらします。エラーチェックツールは、問題を早期に特定し、合成前に信頼性を確保します。合成後、NetListsは、FPGAであろうとASICのいずれであろうと、製造のために準備され、生産の課題を回避するためのデバイス仕様に焦点を当てます。HDLSは、創造性と精度のバランスをとり、革新的でありながら信頼できる回路設計を可能にし、概念から身体的実現まで効率的に進歩します。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

Vitis Unified Softwareプラットフォーム:Xilinxを使用した埋め込みシステムと適応コンピューティングの加速

01/7/2025で公開されています

VLSIテクノロジーの進化と戦略的進歩

01/6/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/17/8000で公開されています 147721

-

USB-Cピンアウトと機能

04/17/2000で公開されています 111791

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/17/1600で公開されています 111328

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/17/0400で公開されています 83653

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79376

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66809

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 62968

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 62865

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54050

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52032