EPM7128SQI100-10 CPLD とデジタル ロジックの処理方法について学ぶ

ボードに余分な部品を詰め込まずに、複数のロジック タスクを処理できる単一のデバイスが必要になることがよくあります。EPM7128SQI100-10 は、制御ロジック、デコード、信号ルーティングを 1 つのプログラマブル チップに組み合わせることで、その柔軟性を実現します。回路のニーズに合わせて動作を形成し、状況が変わった場合には後で調整することができます。バランスのとれたロジック容量と予測可能なタイミングにより、安定したデジタル制御を必要とするシステムによく適合します。表面実装パッケージは、レイアウトをきれいに保ちながら、使用可能な I/O 接続を十分に提供するのにも役立ちます。カタログ

EPM7128SQI100-10の概要

の EPM7128SQI100-10 は、電子システム内のカスタム デジタル制御およびインターフェイス タスクを処理するように設計されたプログラマブル ロジック デバイスです。128 個の論理要素が含まれており、複数の論理機能を 1 つのコンポーネントに組み合わせることができるため、回路レイアウトの簡素化と部品数の削減に役立ちます。このデバイスは、タイミング制御、信号ルーティング、意思決定ベースの操作に適した高速ロジック応答をサポートします。100 ピン表面実装パッケージにより、安定した電気的性能を維持しながら、コンパクトな基板設計への統合が可能になります。一般的な用途には、産業および組み込みアプリケーションでのグルー ロジック、状態制御、アドレス デコード、インターフェイスの適応などが含まれます。EPM7128SQI100-10をお探しですか?現在の在庫、納期、価格を確認するにはお問い合わせください。

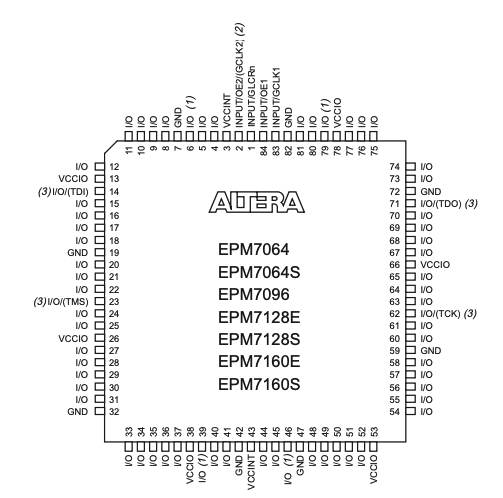

EPM7128SQI100-10のピン配列図

84 ピン PLCC パッケージのピン配置が示されており、信号名とピン番号がデバイスの 4 つの側面すべてに均等に配置されています。ユーザー IO ピンはほとんどの位置を占め、安定した動作をサポートするために専用の電源、グランド、および制御ピンが点在しています。VCC ピンと GND ピンは一定の間隔で配置され、パッケージ全体に一貫した電力分配を提供します。グローバルクロック、出力イネーブル、およびJTAG機能の専用ピンには、汎用I Oと区別するために明確にラベルが付けられています。この図は、予測可能な信号配線、簡素化された基板設計、および関連するMAX 7000シリーズデバイス間の互換性をサポートする標準化されたレイアウトを反映しています。

EPM7128SQI100-10の特長

インシステム プログラマブル ロジック アーキテクチャ

EPM7128SQI100-10 は、回路基板に実装された状態でロジック プログラミングを直接サポートします。これにより、開発中または展開後にデバイスを取り外さずにロジックを更新できます。これにより、ダウンタイムが削減され、システム動作の調整が必要な場合の修正が簡素化されます。

中密度のロジック容量

このデバイスは 128 個のマクロセルを備えており、単一コンポーネント内で複数の論理機能を実装できます。この能力は、追加の個別ロジック デバイスの必要性を減らしながら、制御ロジック、デコード タスク、およびインターフェイス処理をサポートします。

構造化ロジックアレイのブロック設計

8 つの内部ロジック アレイ ブロックにより、ロジック リソースが予測可能な方法で編成されます。この構造は、さまざまな動作条件にわたって安定した信号ルーティングと一貫したロジック動作をサポートします。

使用可能なロジックゲートの可用性

約 2500 の使用可能な論理ゲートを備えたこのデバイスは、ステート マシン、タイミング制御、カスタム デジタル機能をサポートできます。このレベルの統合により、基板レイアウトが簡素化され、全体のコンポーネント数が削減されます。

柔軟なユーザー入力および出力のサポート

このデバイスは、最大 84 個のユーザー設定可能な入出力ピンをサポートします。この柔軟性により、組み込みシステム内の幅広い外部信号、バス、周辺機器とのインターフェースが可能になります。

高速伝播遅延性能

最大伝播遅延が 10 ns であるため、デバイスは入力の変化に迅速に応答できます。そのため、予測可能なタイミングと応答性の高いデジタル制御を必要とするアプリケーションに適しています。

工業用温度動作範囲

このデバイスは、工業用温度範囲全体で確実に動作するように設計されています。これにより、制御システムや産業用電子機器など、温度変化が予想される環境でも安定した性能を発揮します。

EPM7128SQI100-10 技術仕様

| 製品の属性 | 属性値 |

| メーカー | インテル |

| 電圧供給 - 内部 | 4.5V~5.5V |

| サプライヤーデバイスパッケージ | 100-PQFP (20x14) |

| シリーズ | MAX® 7000S |

| プログラマブルタイプ | システムプログラマブルで |

| パッケージ・ケース | 100-BQFP |

| パッケージ | トレイ |

| 動作温度 | -40℃~85℃(TA) |

| マクロセルの数 | 128 |

| ロジックエレメント/ブロック数 | 8 |

| I/O数 | 84 |

| ゲート数 | 2500 |

| 取付タイプ | 表面実装 |

| 遅延時間 tpd(1) Max | 10ns |

| 基本製品番号 | EPM7128 |

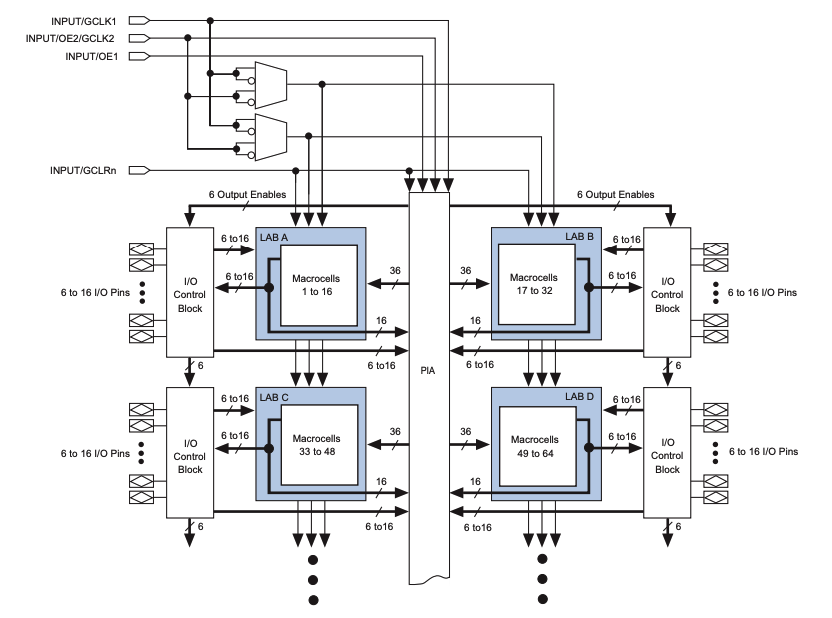

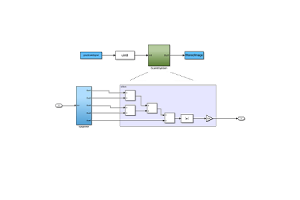

EPM7128SQI100-10のデバイスブロック図

内部アーキテクチャは複数の論理アレイ ブロックを中心に配置されており、各論理アレイ ブロックには、組み合わせおよび登録された論理関数を実装するために使用される定義済みのマクロセルのグループが含まれています。これらのロジック アレイ ブロックは、中央のプログラマブル インターコネクト アレイを介して相互接続されており、予測可能なタイミング動作でブロック間の信号ルーティングを可能にします。専用の IO 制御ブロックがロジック アレイ ブロックを囲み、入力バッファリング、出力駆動、トライステート制御、および外部ピンと内部ロジック間のフィードバック パスを管理します。クロック入力、出力イネーブル信号、グローバル クリア信号などのグローバル リソースはデバイス全体に分散され、同期動作と出力の調整された制御をサポートします。この構造は、EPM7128SQI100-10 で使用される構成を反映しており、複数のロジック アレイ ブロックとマクロセルを統合して、確定的な信号ルーティングと集中制御パスを備えた中密度プログラマブル ロジックをサポートします。

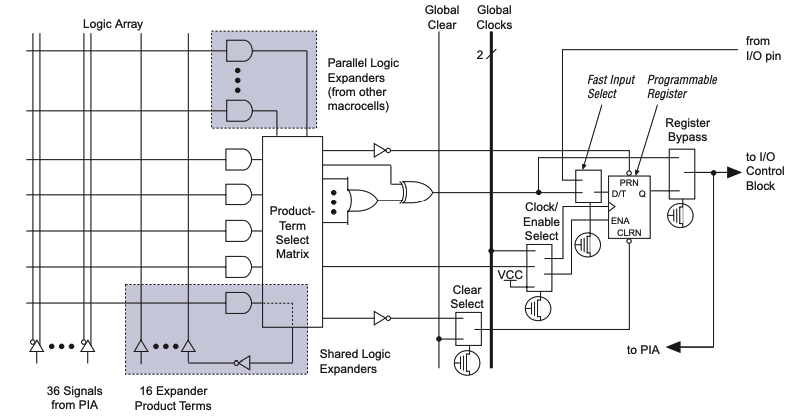

EPM7128SQI100-10のデバイスマクロセル

単一マクロセル内のロジックは、プログラマブル インターコネクト アレイおよびローカル ロジック エクスパンダから入力信号を受け取る積項選択マトリックスを中心に構成されています。複数の積項を組み合わせて積和ロジックを形成し、組み合わせ出力またはプログラマブル レジスタのいずれかを駆動できます。レジスタにはクロック イネーブル、クリア、プリセット、およびバイパス パスが含まれており、登録済み動作と未登録動作の間で柔軟に選択できます。グローバル クロックおよびグローバル クリア信号はマクロセルに直接ルーティングされ、デバイス全体の同期制御をサポートします。出力データは IO 制御ブロックに渡されるか、相互接続アレイにフィードバックされるため、ロジック結果の再利用と EPM7128SQI100-10 内での効率的な信号分配が可能になります。

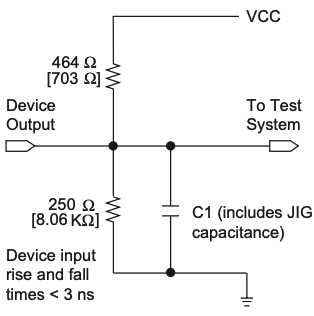

EPM7128SQI100-10のACテスト条件

テスト構成では、抵抗負荷、容量負荷、およびデバイスとテスト システム間の信号パスを指定することにより、AC タイミング測定に使用される電気的条件を定義します。デバイスの出力は、プルアップ抵抗を介して VCC に接続され、スイッチング中の出力駆動動作をモデル化する定義された負荷ネットワークを介してグランドに接続されます。コンデンサは、フィクスチャ効果を含む総負荷容量を表し、テスト システム接続は信号遷移を監視します。一貫した測定条件を保証するために、入力の立ち上がり時間と立ち下がり時間は 3ns 未満に制限されています。このセットアップは、電源過渡現象とグランド電流が観察された AC 性能にどのような影響を与えるかを反映し、EPM7128SQI100-10 のタイミング特性評価のための標準化された条件を確立します。

EPM7128SQI100-10の用途

産業用制御および自動化システム

EPM7128SQI100-10 は、シーケンス、インターロック ロジック、および信号調整を処理するために産業用制御環境で一般的に使用されます。アクチュエーターや制御モジュール用の安定した制御信号を生成しながら、センサーやスイッチからの入力条件を管理するのに役立ちます。そのプログラム可能な構造により、システム要件の変化に応じて制御動作を適応させることができます。

通信機器制御ロジック

電気通信機器では、デバイスはタイミング、信号ルーティング、インターフェイス調整を管理する制御パスをサポートします。これは、処理ユニットと通信インターフェイス間の制御信号を整理するためによく使用され、スイッチングおよび送信ハードウェア内で秩序あるデータ フローを維持するのに役立ちます。

ネットワーキング ハードウェア グルー ロジック

このデバイスは、ネットワーク ハードウェアのグルー ロジックとして適用され、プロセッサ、メモリ デバイス、周辺コンポーネントを接続します。アドレス デコード、バス アービトレーション、信号アラインメントをサポートしており、コンパクトなネットワーク システム内でさまざまなデジタル ブロックを一緒に動作させることができます。

組み込みシステム インターフェイスとデコード ロジック

EPM7128SQI100-10 は、組み込みシステム内で、コントローラと外部デバイス間のインターフェイス ロジックを提供します。これは、アドレスのデコード、制御信号の生成、および基本的なプロトコルの処理に使用され、システム設計を簡素化し、個別のロジック コンポーネントの数を減らすのに役立ちます。

レガシー コンピューティングおよび計測システム

このデバイスは、安定したロジックの交換を必要とするレガシー コンピューティング プラットフォームや計測システムに最適です。既存の信号レベルやタイミング動作との互換性を維持しながら、古い個別のロジック機能を単一のプログラマブル デバイスに統合できます。

プロトコルブリッジングとステートマシンの実装

EPM7128SQI100-10 は、構造化されたデジタル プロセスを管理するプロトコル ブリッジングとステート マシンを実装するために使用されます。定義された状態遷移と制御シーケンスをサポートしており、異なるシステム ブロック間での通信と制御タスクの調整に適しています。

EPM7128SQI100-10のメリットとデメリット

利点

• ボードからデバイスを取り外さずにシステムロジックのアップデートをサポート

• 中規模の制御およびインターフェイスロジックに適した 128 個のマクロセルを提供

• 最大10nsの伝播遅延で予測可能なタイミングを実現

• 工業用温度範囲全体で動作し、安定したフィールドパフォーマンスを実現

• 柔軟なインターフェースを実現する多数のユーザー構成可能な入出力ピンが含まれています。

短所

• 5 V 電源で動作するため、低電圧システムとの互換性が制限されます。

• 最近のプログラマブル ロジック デバイスと比較してロジック容量が低い

• 電力使用量は、最新の低電力プログラマブル代替製品よりも高い

• パッケージサイズが非常にコンパクトな設計やスペースに制約のある設計に適さない可能性があります。

EPM7128SQI100-10の代替品

| 部品番号 | メーカー | 主な特長 | 使用例/注意事項 |

| EPM7128SQI100-10N | インテル | システム内プログラマビリティ、5 V の内部電源範囲、最大 10 ns の高速伝播遅延を備えた 128 個のマクロセルを表面実装パッケージに収めています。 | 信頼性の高いタイミングと適度なロジック密度を必要とするデジタル グルー ロジック、制御ロジック、およびインターフェイス アプリケーションで使用されます。 |

| EPM7128SQI160-10 | インテル | 10 ns のスピード グレードを備えた同じ 128 マクロセル アーキテクチャを、配線の柔軟性を拡張するためにより大きなピン数のパッケージで提供します。 | 追加の I/O アクセスや既存のボード レイアウトとの互換性が必要な設計に最適です。 |

| EPM7128SQI160-10N | インテル | 128 個のマクロセル、安定した 5 V 動作および拡張温度サポートを備えたシステム内プログラム可能な CPLD。 | より広い温度範囲にわたって信頼性の高いロジック制御を必要とする産業および組み込みシステムに適しています。 |

インテルについて

インテルは、幅広いデジタル コンピューティングおよびプログラマブル ロジック ソリューションの開発で知られる世界的なテクノロジー企業です。同社には、コンピューティング、通信、組み込みシステム向けの半導体設計を進歩させてきた長い歴史があります。そのプログラマブル ロジック ポートフォリオは、産業用、ネットワーキング、組み込みアプリケーションにわたるシステム制御、信号管理、インターフェイス ロジックをサポートします。インテルは、パフォーマンス、安定性、長期的なプラットフォーム サポートのバランスをとったスケーラブルなロジック プラットフォームの提供に重点を置いています。その製品は、確立されたシステム アーキテクチャと進化するデジタル設計の両方で広く使用されており、より広範なエレクトロニクス エコシステムにおける強い存在感を反映しています。

結論

EPM7128SQI100-10 は、ロジック制御、タイミング、インターフェイス処理を 1 つのプログラマブル デバイスに統合します。論理配列ブロックとマクロセルを含む明確な構造が得られ、動作が予測可能になります。ピン レイアウトと I/O の柔軟性により、ボードの配線が簡素化されます。高速な応答時間により、多くのシステムで安定したデジタル制御がサポートされます。このデバイスは、ハードウェアを変更せずにロジックを更新する必要がある場合にも機能します。全体として、中規模のデジタル ロジックを 1 か所で管理する実用的な方法を提供します。

データシートPDF

EPM7128SQI100-10 データシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1. EPM7128SQI100-10 はどのようなタイプのデバイスですか?

これは、制御、デコード、信号ルーティングなどのカスタム デジタル ロジック機能を実行するようにプログラムできる CPLD です。

2. EPM7128SQI100-10 にはマクロセルがいくつありますか?

このデバイスには 128 個のマクロセルが含まれており、複数の論理機能を 1 つのチップに組み合わせることができます。

3. インストール後にロジックを更新できますか?

はい、インシステム プログラミングをサポートしているため、デバイスがボードにマウントされている間にロジックを更新できます。

4. このデバイスはどのようなパッケージを使用していますか?

コンパクトな PCB 設計に適した 100 ピン表面実装パッケージで提供されます。

5. EPM7128SQI100-10 はどこで一般的に使用されますか?

これは、組み込みおよび産業システムにおける制御ロジック、グルー ロジック、ステート マシン、インターフェイス処理によく使用されます。

AD9883AKST-140 高解像度ディスプレイ用アナログビデオ ADC

01/6/2026で公開されています

トリムポットとは何か、そしてその仕組み

01/6/2026で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/19/8000で公開されています 147781

-

USB-Cピンアウトと機能

04/19/2000で公開されています 112056

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/19/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/19/0400で公開されています 83811

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79624

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66995

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63119

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63057

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54097

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52207