DIPの理解:説明したデュアルインラインパッケージ

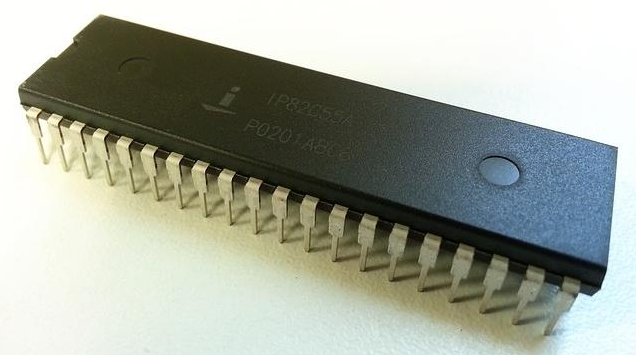

デュアルインラインパッケージ(DIP)CPUチップは、マイクロエレクトロニクスの鍵であり、アセンブリを簡素化し、汎用性を保証する実用的で信頼できるデザインを提供します。平行ピンのデュアル列により、これらのチップは回路基板設計の初期であり、ソケットの挿入やはんだ付けが簡単になりました。時間が経つにつれて、DIPパッケージは、特定のニーズのための多様な構成、材料、およびシーリング方法に適合しています。この記事では、DIPの基本、その歴史的重要性、および最新の電子機器におけるそれらの継続的な役割、構造、PIN構成、アプリケーション、およびデリバティブパッケージをカバーする継続的な役割について説明します。プロトタイピングであろうとレガシーシステムの研究であろうと、DIPテクノロジーの永続的な影響を発見してください。カタログ

概要

DIP(デュアルインラインパッケージ)CPUチップは、ピンの2つの平行な列を備えた独特のデザインで際立っています。この思慮深いエンジニアリングにより、互換性のあるチップソケットへのスムーズな挿入や、はんだ穴の構成が一致する回路基板への直接取り付けが可能になります。これらのチップを挿入して削除するプロセスには、慎重に注意する必要があります。誤っても、ピンの損傷が発生する可能性があり、その後、機能の問題や完全なチップ障害につながる可能性があります。

ディップパッケージは特異なエンティティではありません。多層セラミック、シングルレイヤーセラミック、リードフレームタイプなど、さまざまな構成で構成されています。これらのバリエーションのそれぞれは、さまざまなアプリケーションのパフォーマンスと適合性に大きな影響を与える可能性のある独自の特性セットをもたらします。たとえば、多層セラミックパッケージは、例外的な電気性能と熱安定性により、多くの場合、高周波アプリケーションで好ましい選択です。逆に、プラスチックのカプセル化は、大量生産のための予算に優しいオプションとして機能し、パフォーマンスとコストの考慮事項のバランスを効果的にバランスさせます。

さらに、ガラスセラミックシーリングや低溶融ガラスパッケージなど、パッケージング方法の選択は、チップの寿命と信頼性に有意に影響します。たとえば、ガラスセラミックシーリングは、環境の課題に対する顕著な保護を提供し、それにより、要求の厳しい条件でのチップの耐久性を高めます。この側面は、CHIPが自動車や航空宇宙セクターなど、極端な温度や水分に耐える業界で特に重要になります。

ディップのアプリケーション

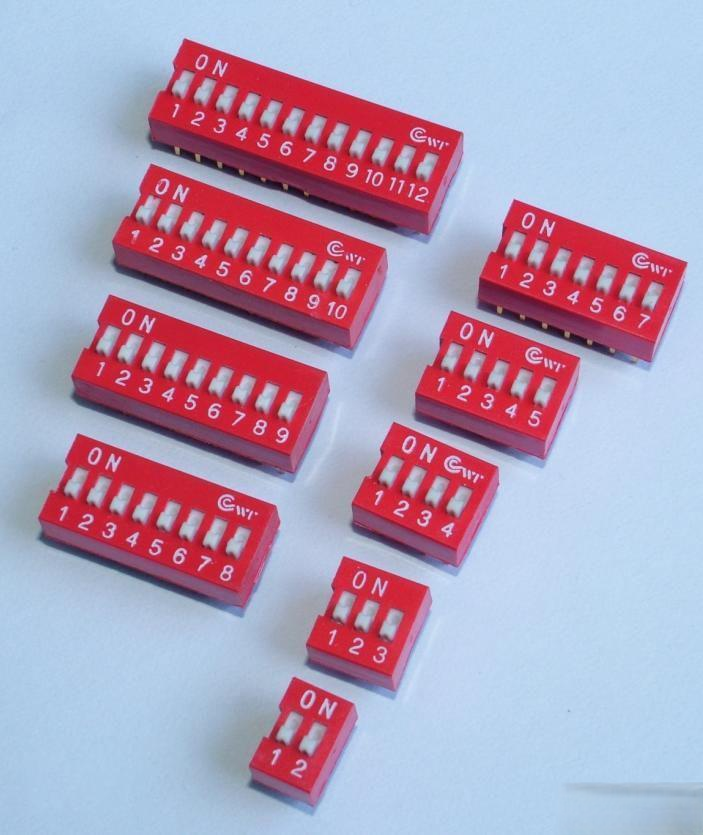

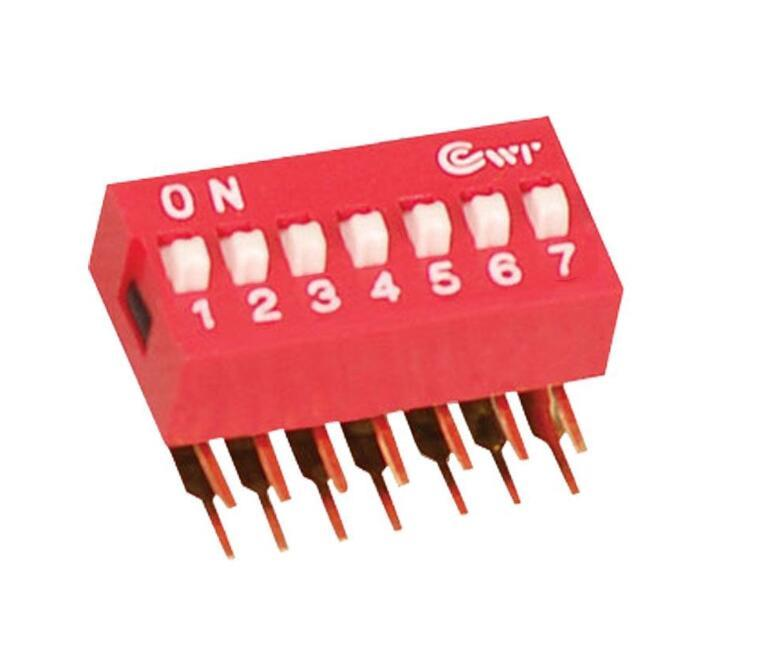

DIP(デュアルインラインパッケージ)パッケージは、ディップスイッチ、LED、7セグメントディスプレイ、棒グラフディスプレイ、リレーなどの幅広いコンポーネントを含む統合回路の初期要素です。1964年に14ピンのバリアントを備えたExpress半導体のBryant Buck Rogersによって導入された長方形の設計は、古いラウンドコンポーネントと比較してコンパクトで効率的な配置を提供しました。ディップコネクタは、コンピューターおよび電子ケーブルシステムの基本的なものにもなり、その多様性と広範な使用が強化されました。

ディップパッケージの設計は、自動アセンブリプロセスに優れており、複数の統合回路を同時に処理するための波のはんだ付けなどの効率的な手法を可能にし、手動労働を大幅に削減します。ブレッドボードとの互換性により、プロトタイピングに必要になり、デザインの反復中にコンポーネントを簡単に交換できます。この適応性により、さまざまなアプリケーションでの人気が保証されました。これは、主に1970年代と1980年代にディップパッケージがマイクロエレクトロニクスの景観を支配していました。

ただし、業界が進化するにつれて、PLCCやSOICなどの表面マウントパッケージは、大量生産効率でDIPを上回りました。これらの新しい形式はブレッドボードとの互換性が低いですが、アダプターはSurface-Mount Devices(SMDS)がDIP構成に統合できるようになり、現代のテクノロジーに従来のプロトタイピングニーズを埋めます。外部プログラミングデバイスとの互換性により、EPROMやGALSなどのプログラム可能なコンポーネントには、DIPパッケージが歴史的に好まれていましたが、インシステムプログラミング(ISP)およびコンパクトデザインへのシフトは、業界を反映した表面マウント形式に新しいプログラム可能なコンポーネントを主に遷移しました。小型化と効率に焦点を当てます。

ディップの構造

DIP(デュアルインラインパッケージ)チップは、主にプラスチックまたはセラミック素材のいずれかに包まれており、それぞれがさまざまなアプリケーション要件に合わせて調整されたユニークな利点を提供します。セラミックパッケージは、卓越した気密性に対して主に尊敬されているため、航空宇宙や医療機器などの高信頼性セクターで好まれる選択肢となっています。これらの環境は、顕著な耐久性と環境への影響に対する強い抵抗を必要とします。セラミック素材が自然に持っている品質。セラミックエンセースの寿命と安定性により、厳しい状態に直面しても、チップが長期にわたって機能を保持することが保証されます。

一方、ほとんどのディップチップは通常、熱硬化性樹脂プラスチックに収容されています。この材料は、その迅速な処理能力に対して高く評価されており、驚くべき効率でかなりの量のチップを生産することができます。熱硬化プラスチックの迅速な生産能力は、電子部品の需要の増加に対処するだけでなく、ハイテクの進歩の急速に進化する景観とも一致しています。この製造効率は実質的な役割を果たしているため、市場にイノベーションを迅速に導入できるようになり、最先端のテクノロジーに対する消費者の期待に応えます。

さらに、包装材料の選択は、チップの熱および電気性能に大きな影響を与えます。熱硬化プラスチックは大規模な生産に利点がありますが、セラミックが提供する熱伝導率が不足している可能性があります。この側面は、高性能コンピューティングや電力管理システムなど、効果的な熱散逸が必須であるアプリケーションで主に使用されます。その結果、生産効率とパフォーマンスニーズのバランスをとるという課題に頻繁に遭遇し、特定のアプリケーションに最も適した資料に関する継続的な議論を引き起こすことができます。

ピンの数とディップのピッチ

|

パラメーター |

詳細 |

|

ピッチ(ピン間隔) |

- 一般:0.1インチ(2.54 mm) |

|

- あまり一般的ではない:0.07インチ(1.778 mm) |

|

|

行間隔 |

- 一般:0.3インチ(7.62 mm)、0.6インチ(15.24 mm) |

|

- あまり一般的ではない:0.4インチ(10.16 mm)、0.9インチ(22.86

mm)、0.75インチ(19.05 mm) |

|

|

メトリックピッチ |

- ソビエト/東ヨーロッパの標準:2.5 mm |

|

ピンの数(0.3インチの間隔) |

- 共通:8、16、20、24 |

|

- レア:4、28 |

|

|

ピンの数(0.6インチの間隔) |

- コモン:24、28、32、40 |

|

- レア:36、48、52 |

|

|

ピンの最大数 |

-Motorola 68000およびZilog Z180 CPU:64ピン |

ディップの方向とピン数

コンポーネントの識別ノッチが上方に配置されると、左上にあるピンはピン1としてマークされます。残りのピンには反時計回りの方向に番号が付けられます。この体系的な方法は、正しい接続を確立し、統合回路(IC)の機能を確保する上で顕著な役割を果たします。たとえば、DIP14 ICでは、ピン1は上部の左側に位置し、ピン1〜7が左に降り、ピン8〜14が右に上昇します。

ピンの向きを把握することは、効果的な電子回路の設計と実装のためにアクティブです。ピンの誤認されると、接続が誤っている可能性があり、回路の故障やコンポーネントの損傷を引き起こす可能性があります。これは、アセンブリプロセス中の細部への細心の注意の必要性を強調しています。多くの場合、コンポーネントをPCBにはんだ付けする前に、データシートでPIN構成を相互参照する慣行を育てることができます。このような勤勉さは、エラーの可能性を減らすだけでなく、最終製品の全体的な信頼性にも貢献します。

PIN番号のシステムは、さまざまなコンポーネント間の相互運用性を促進する標準として機能します。提供されたピンアウト図に慣れることは、回路を設計するときに有利であることがわかります。これらの図は、視覚補助剤として機能し、各ピンの機能が対応する数字とともに明確に描写されています。さらに、プロトタイピング中にPIN構成をラベル付けおよび文書化するための一貫した方法を維持することで、トラブルシューティングと将来の変更を大幅に促進できます。

さらなる派生パッケージ

SOIC(Small Outline IC)パッケージは、消費者の電子機器やパーソナルコンピューターで主に好まれている広く受け入れられている表面マウントテクノロジーとして際立っています。その設計は、標準のPDIP(プラスチックデュアルインラインパッケージ)のよりコンパクトなバリエーションであり、スペース効率を最大化するために両側に配置されたピンを備えています。この思慮深いデザインは、コンパクトさが単なる好みではなく、消費者の需要によって推進される必要性である現代の電子化における小型化に向かう成長傾向に共鳴します。

SOICに加えて、他の同様のパッケージング方法が業界の状況に貢献しています。これらには以下が含まれます:

• soj(小さなアウトラインJリード):多くの場合、メモリデバイスに選択されたSOJパッケージは、接続性とパフォーマンスの両方を強化する特定のPIN構成を備えています。

• SOP(小さなアウトラインパッケージ):SOPパッケージは、多種多様なピンカウントとサイズを提供することで知られており、多数のアプリケーションで汎用性を提供します。

パッケージタイプを選択すると、さまざまなデザインの考慮事項が機能し、それぞれに独自の意味があります。

• 熱性能:熱を効果的に消散するパッケージの容量が支配的です。不十分な熱管理は、デバイスの信頼性を危険にさらす可能性があります。

• 物質的な選択:材料の選択は、パッケージの全体的な完全性と寿命において重要な役割を果たします。

• ピンレイアウト:ピンの配置は、密集した回路板で動的である電磁干渉(EMI)特性に大きく影響する可能性があります。

これらの要因を慎重に観察することにより、現在の技術的要求を満たすだけでなく、時の試練に耐えるより回復力のあるパッケージを作成できます。

ディップパッケージの機能

|

特徴 |

説明 |

|

操作の容易さ |

PCBでの穴あきとはんだ付けに適しています(印刷

回路基板)、操作しやすい。 |

|

チップ対パッケージエリアの比率 |

チップ領域とパッケージエリアの比率は

大きく、より大きなボリュームになります。 |

|

CPUでの歴史的使用 |

4004、8008、8086などの初期のCPUで使用され、

8088。ピンの2列をマザーボードスロットに挿入するか、はんだ付けできます

直接。 |

|

メモリ粒子の人気 |

メモリ粒子が直接接続された時代

マザーボードには、ディップパッケージが広く使用されていました。 |

|

SDIP(Shrink Dip)誘導体 |

と比較して、ピン密度の6倍を提供します

従来のディップパッケージ。 |

|

スイッチとして浸します |

DIPは、特定の電気を使用したDIPスイッチも指します

特性: |

|

- 電気寿命:24VDC電圧でテストされました

25MA電流、最大2000のトグルまで続きます。 |

|

|

- 定格電流(頻繁に切り替えない):100mA、

50VDCに耐えます。 |

|

|

- 定格電流(頻繁に切り替えられた):25ma、

耐性24VDC。 |

|

|

- インピーダンスの連絡先:(a)初期値:最大50mΩ;(b)

テスト後の値:最大100mΩ。 |

|

|

- 絶縁抵抗:500VDCでの最小100mΩ。 |

|

|

- 圧縮強度:500VAC 1分間。 |

|

|

- 極静電容量:最大5pf。 |

|

|

- ループタイプ:単一連絡先単一選択:DS(s)、

DP(L)。

|

DIP(デジタル画像プロセッサ)2D画像

ディップパッケージチップの利用

ピンのデュアル列によって識別可能なDIPパッケージチップは、さまざまな電子システムに組み込むための柔軟なソリューションを提示します。これらのチップは、ディップソケットに簡単にはんだ付けするか、回路基板に直接はんだ付けできます。穴のはんだ付けのこの方法は、アセンブリプロセスを簡素化するだけでなく、学習と実験の実践的な性質と共鳴します。このような使いやすさは、教育環境とプロトタイピングシナリオでほとんど有利です。このシナリオでは、デザインを迅速に反復する能力が非常に高く評価されています。

それにもかかわらず、ディップパッケージの設計はマザーボードとの互換性を促進しますが、いくつかの課題が考慮事項を保証します。これらのパッケージのフットプリントが大きくなり、厚さが増加すると、人口密度の高い回路基板に空間的な制限が生じる可能性があります。さらに、露出したピンは、取り扱い中に損傷を受けやすく、接続の信頼性を潜在的に露出させる可能性があります。実践的な経験は、慎重な取り扱い慣行と、抗静止バッグの使用などの保護対策が、これらの懸念を軽減するのに役立つことを示しています。

通常、ディップパッケージは最大100ピンを収容し、機能性と製造可能性の間の思慮深いバランスを反映しています。CPU統合の進歩が進むにつれて、ディップパッケージの有病率が衰退し、よりコンパクトで効率的なパッケージング技術が得られました。この移行は、エレクトロニクス業界の小型化と強化された統合に向けてより広範な傾向を意味し、空間を保護しながらパフォーマンスを改善することを目指しています。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

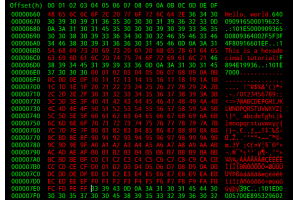

ヘックス:デジタルシステムの言語

12/30/2024で公開されています

電子機器の乗数:原則、種類、およびアプリケーション

12/30/2024で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/18/8000で公開されています 147749

-

USB-Cピンアウトと機能

04/18/2000で公開されています 111886

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/18/1600で公開されています 111349

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/18/0400で公開されています 83712

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79497

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66864

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63000

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 62921

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54070

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52086