XC2S200-5FG256I FPGA アーキテクチャとアプリケーションの理解

システムが必要とする通りにデジタル ハードウェアを正確に形成できるプログラマブル ロジック デバイスを探しているかもしれません。XC2S200-5FG256I FPGA は、柔軟なロジック ブロック、内部メモリ、および多数の入出力接続を提供するため、1 つのデバイス内にカスタム デジタル機能を構築できます。そのアーキテクチャは、さまざまな種類の電子機器にわたる信号ルーティング、タイミング制御、インターフェイス処理をサポートします。チップ上で利用可能なプログラム可能なルーティングとメモリ リソースを使用すると、物理ハードウェアを変更せずに、チップをさまざまな制御タスク、通信パス、組み込みシステム機能に適応させることができます。カタログ

XC2S200-5FG256I 概要

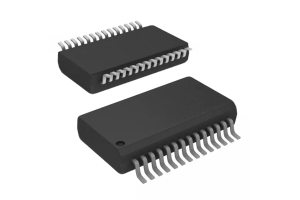

の XC2S200-5FG256I は、Spartan II FPGA アーキテクチャに基づいて構築され、構成可能なデジタル システム用に設計されたプログラマブル ロジック デバイスです。カスタム デジタル機能を実装するようにプログラムできる、構成可能な論理ブロックを通じて配置された約 200,000 個の論理ゲートを提供します。統合ブロック RAM は一時的なデータ ストレージをサポートし、多数の入出力ピンにより外部コンポーネントとの柔軟な通信が可能になります。このデバイスは低電圧コア電源で動作し、工業用温度条件をサポートします。そのアーキテクチャは、組み込み電子機器におけるハードウェアのプロトタイピング、インターフェイス制御、およびデジタル処理タスクをサポートします。

XC2S200-5FG256Iをお探しですか?現在の在庫、納期、価格を確認するにはお問い合わせください。

XC2S200-5FG256I b

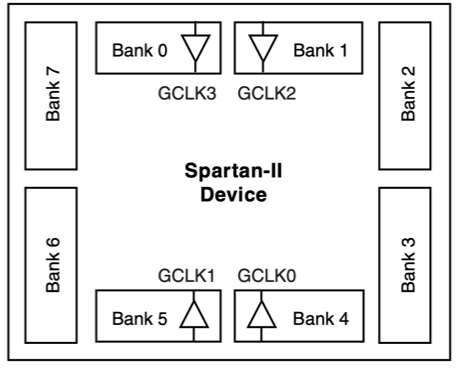

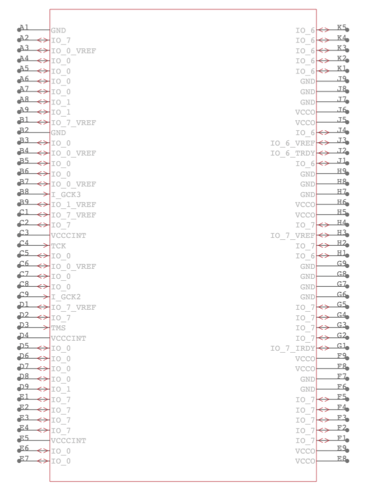

I/O 構造は、FPGA パッケージの 4 つの側面すべてに沿って配置された 8 つのバンクにデバイスの周囲を分割します。各バンクは、同じ VCCO 電源を共有する入力ピンと出力ピンのセットをグループ化し、その領域内のすべてのピンに一貫した電圧レベルを適用できるようにします。GCLK0 ~ GCLK3 とラベル付けされたグローバル クロック入力は、クロック信号を内部ロジック アレイ全体に均等に分配するために、レイアウトの下部セクションと上部セクションの近くに配置されます。この構成により、外部ピンと内部プログラマブル ロジック間の組織的な配線を維持しながら、異なる電圧レベルを個別のバンクに割り当てることで、複数の信号規格を同時に動作させることができます。

XC2S200-5FG256I CADモデル

XC2S200-5FG256I 記号

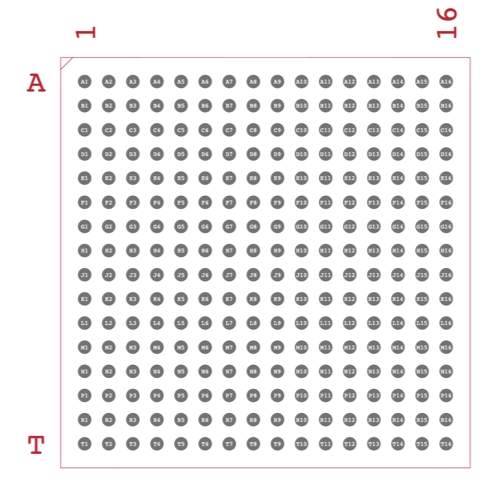

XC2S200-5FG256I フットプリント

XC2S200-5FG256I 3Dモデル

XC2S200-5FG256Iの特長

プログラマブル FPGA ロジック アーキテクチャ

このデバイスは構成可能な論理構造を使用しており、プログラマブルな論理ブロックと配線パスを通じてデジタル回路を定義できます。この構造により、設計者は物理デバイスを変更せずにカスタム ハードウェア動作を実装でき、柔軟なデジタル システム開発とハードウェア プロトタイピングをサポートします。

統合されたブロックメモリリソース

内部ブロック RAM は、プログラマブル ファブリック内に専用のメモリ ストレージを提供します。これらのメモリ ブロックは、データ バッファリング、ルックアップ テーブル、および一時ストレージ操作をサポートし、多くのデジタル処理アプリケーションにおける外部メモリ コンポーネントの必要性を軽減します。

構成可能な入力および出力インターフェイス

最大 176 個のユーザー入出力ピンにより、外部デバイスとの柔軟な接続が可能になります。各ピンはさまざまな入力、出力、または双方向機能用に構成でき、デバイスがセンサー、通信インターフェイス、および制御システムと対話できるようになります。

プログラマブル ルーティング ネットワーク

プログラマブル相互接続ネットワークは、論理ブロック、メモリ要素、および入出力インターフェイスをリンクします。信号は構成可能なパスを介してルーティングできるため、予測可能なデジタル動作を維持しながら、内部リソース間のカスタム信号フローが可能になります。

遅延ロックループを使用したクロック管理

統合された遅延ロック ループ回路は、デバイス内のクロック分配とタイミング調整をサポートします。これらの回路は、内部ロジック セクションと外部クロック ソース間の安定したタイミング関係を維持するのに役立ちます。

工業用温度動作能力

このデバイスは、産業環境に適した拡張温度範囲にわたる動作をサポートします。これにより、工場設備や屋外設置など、さまざまな環境条件にさらされるシステムでも安定した性能を発揮します。

コンパクトな表面実装 BGA パッケージ

このデバイスは、コンパクトな設置面積で多数の接続を可能にする 256 ボール グリッド アレイ形式でパッケージ化されています。このパッケージ スタイルは、ピン数の多いデバイスの電気的信頼性を維持しながら、高密度のプリント基板レイアウトをサポートします。

XC2S200-5FG256I 技術仕様

| 製品の属性 | 属性値 |

| メーカー | AMDザイリンクス |

| 電圧 - 電源 | 2.375V~2.625V |

| 合計RAMビット数 | 57344 |

| サプライヤーデバイスパッケージ | 256-FBGA (17x17) |

| シリーズ | Spartan®-II |

| パッケージ・ケース | 256-BGA |

| パッケージ | トレイ |

| 動作温度 | -40℃~100℃(TJ) |

| ロジックエレメント/セルの数 | 5292 |

| LAB/CLB の数 | 1176 |

| I/O数 | 176 |

| ゲート数 | 200000 |

| 取付タイプ | 表面実装 |

| 基本製品番号 | XC2S200 |

| RoHS ステータス | RoHS非対応 |

| 感湿性レベル (MSL) | 3 (168 時間) |

| リーチステータス | REACHは影響を受けない |

| ECCN | EAR99 |

| HTSUS | 8542.39.0001 |

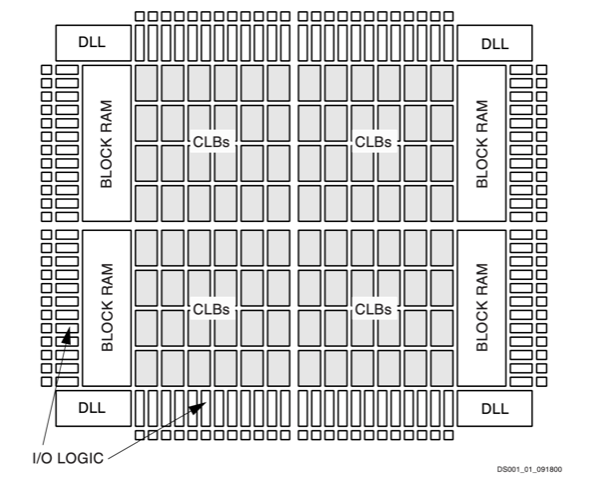

XC2S200-5FG256Iのブロック図

構成可能なロジック ブロックの中央グリッドは、ルックアップ テーブルとフリップ フロップを使用してデジタル機能が実装されるプログラマブル ロジック ファブリックを形成します。ブロック RAM とラベル付けされた垂直列は、データ ストレージとバッファリング操作のためにロジック アレイの横に配置された組み込みメモリ リソースを提供します。入力および出力ロジック ブロックはデバイスの外縁に並び、内部ルーティング ネットワークを外部ピンに接続します。コーナーに配置された遅延ロック ループ ユニットは、内部ロジック構造全体にわたるクロック アラインメントとタイミング制御をサポートします。CLB アレイ、メモリ列、クロック ユニット、および IO ブロック間の相互接続パスは、デバイス全体で柔軟な信号接続を可能にするプログラム可能なルーティング ネットワークを作成します。

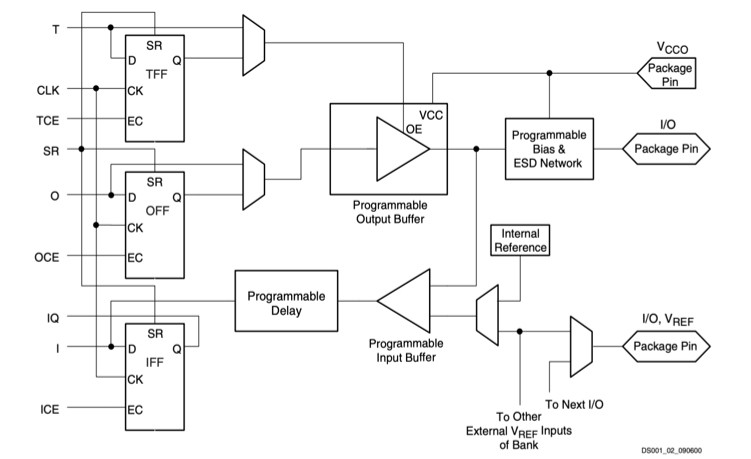

XC2S200-5FG256Iの入出力ブロック(IOB)

内部 I/O ブロック構造は、構成可能な入出力パスを介して外部パッケージ ピンをプログラマブル ロジック ファブリックに接続します。出力データは、クロックおよびイネーブル制御を備えた「OFF」とラベル付けされたフリップフロップを通過し、その後、I O バンクに関連付けられた VCCO 電源で動作しながら外部ピンを駆動するプログラマブル出力バッファを通過します。パッケージ ピンからの入力信号は、プログラマブル入力バッファとオプションのプログラマブル遅延ステージを通過し、信号を内部クロックと同期させる IFF というラベルの付いた入力フリップフロップに到達します。追加の制御要素には、TFF レジスタを介したトライステート制御、クロック イネーブル信号、信号のタイミングと状態制御を管理するセット リセット入力が含まれます。プログラム可能なバイアスと ESD 保護ネットワークがピン インターフェイスを保護し、内部リファレンスと VREF 接続がバンク全体で共有される電圧リファレンスの IO 規格をサポートします。

XC2S200-5FG256Iの用途

デジタル信号ルーティング システム

プログラマブル ロジック リソースにより、デバイスは通信機器におけるデジタル信号のルーティングと処理を管理できます。構成可能なロジック ブロックは、安定したタイミング動作を維持しながらシステム コンポーネント間のデータ転送を処理するカスタム ロジック パスを実装できます。

産業用オートメーション制御ユニット

産業用制御システムでは、多くの場合、さまざまな機械プロセスに適応できる柔軟なデジタル ロジックが必要です。このデバイスは制御信号、センサー入力、アクチュエーター出力を管理し、自動化された生産環境での信頼性の高い動作をサポートします。

組み込みハードウェア プロトタイピング プラットフォーム

開発プラットフォームでは、最終的なハードウェアの製造前にデジタル設計をテストするためにプログラマブル ロジック デバイスを頻繁に使用します。このデバイスを使用すると、設計者は開発中に論理構造を実装および変更できるため、デジタル制御機能の効率的なテストが可能になります。

通信インターフェースブリッジング

複数の通信プロトコルを接続するシステムは、このデバイスを使用して、インターフェイス間でデジタル信号を変換またはルーティングできます。そのプログラマブル ロジックにより、プロセッサ、メモリ デバイス、通信コントローラをリンクするカスタム データ パスが可能になります。

自動車電子サブシステム

車両の電子制御ユニットには、信号管理とシステム調整のためのプログラマブル ロジックが必要です。このデバイスは、自動車エレクトロニクス内のデジタル制御タスク、通信インターフェイス、タイミング機能を処理できます。

民生用電子制御ロジック

デジタル消費者向けデバイスは、多くの場合、システム機能を管理するためにコンパクトなプログラマブル ロジックを必要とします。このデバイスは、ユーザー インターフェイス信号、タイミング制御、電子製品内のコンポーネント間の内部通信を調整できます。

XC2S200-5FG256I の長所と短所

利点

• プログラマブルロジック構造により、設置後にデジタル回路を再構成可能

• 統合ブロック メモリは、一部の設計で外部メモリなしでデータ ストレージをサポートします。

• 多数の入出力ピンにより柔軟なシステム接続をサポート

• 工業用温度条件全体での安定した動作

• コンパクトな BGA パッケージは、高密度のプリント基板レイアウトをサポートします。

• 内部クロック調整回路により、一貫したタイミング動作を維持できます。

短所

• ロジック容量は、最近のプログラマブル デバイスよりも低い

• 最新のプログラマブル ロジック ファミリと比較してオンチップ メモリのサイズが制限されている

• 消費電力は、新しい低電圧アーキテクチャよりも高くなる可能性があります

• 高度な統合信号処理リソースは含まれていません

• デバイスプログラミングには外部設定メモリが必要

XC2S200-5FG256Iの代替品

| 部品番号 | メーカー | 主な特長 | 使用例/注意事項 |

| XC2S200-5FGG256I | AMD | 構成可能なロジック ブロック、分散 RAM、およびプログラム可能な配線リソースを備えた Spartan-II FPGA。2.5 V コア電源付近で動作し、カスタム デジタル回路を実装するための数千のロジック セルを提供します。 | プログラマブル ロジックと工業用温度範囲での信頼性の高い動作が必要な組み込み処理、工業用制御、および通信ハードウェアで使用されます。 |

| XC2S200-5FGG256C | AMD | プログラマブル ロジック エレメント、内部メモリ ブロック、構成可能な I/O 接続を統合して柔軟なデジタル設計を実現する、Spartan-II ファミリの FPGA デバイス。 | 適度なロジック密度と柔軟なハードウェア構成が必要な家庭用電化製品、通信モジュール、プロトタイピング プラットフォームに適しています。 |

| XC2S200-5FG256C | AMD | 構成可能なロジック セル、内部メモリ リソース、ユーザーが構成可能な複数の I/O ピンを備えたプログラマブル FPGA デバイスで、単一チップ上に複雑なデジタル回路を実装します。 | データ収集システム、信号処理プラットフォーム、プログラム可能なデジタル ハードウェアを必要とする組み込み設計に適用されます。 |

| XC2S200-5FGG456I | AMD | ピン数の多い Spartan-II FPGA は、複雑なデジタル システムにプログラマブル ロジック ブロック、組み込みメモリ、および多数の I/O 接続を提供します。 | 産業オートメーション、高度な通信機器、柔軟なプログラマブル ロジックと拡張温度サポートを必要とする高 I/O 組み込みシステムで使用されます。 |

AMDザイリンクスについて

AMD ザイリンクスは、プログラマブル ロジック デバイスとアダプティブ コンピューティング プラットフォームの開発で知られる半導体テクノロジー企業です。同社はザイリンクスとして誕生し、後にアドバンスト マイクロ デバイセズの一部となりました。その研究は、コンピューティング、通信、自動車エレクトロニクス、および産業システムで使用されるフィールド プログラマブル ゲート アレイ、適応型システム オン チップ デバイス、およびプログラマブル アクセラレーション プラットフォームに焦点を当てています。同社は数十年にわたってプログラマブル ロジック アーキテクチャを開発し、製造後に回路を定義できる構成可能なデバイスを通じてデジタル ハードウェア設計をサポートしています。同社の製品は、組み込みシステム、ネットワークインフラ、信号処理装置、電子制御システムなどで広く使用されています。

結論

XC2S200-5FG256I FPGA を使用すると、デジタル ロジックをハードウェアに直接構築する柔軟な方法が得られます。さまざまなシステム タスクをサポートするように、論理ブロック、メモリ リソース、および入出力接続を構成できます。その内部構造により、信号ルーティング、タイミング制御、および単一のプログラマブル デバイス内でのデータ保存が可能になります。XC2S200-5FG256I FPGA アーキテクチャとアプリケーション アーキテクチャを理解した構成可能なデバイスは、組み込み電子機器、通信インターフェイス、および制御システムをサポートできます。そのレイアウト、機能、およびアプリケーションを理解することは、プログラマブル ロジック デバイスが最新のデジタル機器をどのようにサポートしているかを理解するのに役立ちます。これにより、XC2S200-5FG256I が電子設計のニーズに適合するかどうかを評価しやすくなります。

データシートPDF

XC2S200-5FG256I データシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1. XC2S200-5FG256I とはどのようなデバイスですか

XC2S200-5FG256I は、フィールド プログラマブル ゲート アレイです。それは デジタル回路を構成できるプログラマブル ロジック デバイス 固定されたハードウェア設計ではなくソフトウェアを通じて。

2. XC2S200-5FG256I は入力ピンと出力ピンをいくつ備えていますか

XC2S200-5FG256I デバイスは、最大 176 のユーザー構成可能な入力をサポートします および出力ピンにより、多くの外部コンポーネントとの接続が可能になります。 そして通信インターフェース。

3. XC2S200 FPGA のブロック RAM の目的は何ですか?

ブロック RAM は、一時的なデータ ストレージに使用される内部メモリを提供します。 バッファリング、ルックアップテーブル、およびその他のデータ処理タスク プログラマブルロジックシステム。

4. XC2S200-5FG256I はどこで一般的に使用されますか

このデバイスは、組み込み電子機器、通信でよく使用されます。 システム、産業用オートメーション機器、デジタル制御システム プログラマブルなハードウェア ロジックが必要です。

5. XC2S200-5FG256I はどのようなパッケージ タイプを使用しますか

XC2S200-5FG256I は 256 ボール グリッド アレイ形式でパッケージ化されています。 コンパクトな設置面積で多数の接続が可能になります。 高密度の回路基板レイアウトに適しています。

DVI コネクタについて: 知っておくべきことすべて

03/9/2026で公開されています

ADM560JRS インターフェイス チップ ガイド、機能、およびアプリケーション

03/5/2026で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/18/8000で公開されています 147761

-

USB-Cピンアウトと機能

04/18/2000で公開されています 111984

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/18/1600で公開されています 111351

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/18/0400で公開されています 83743

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79536

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66946

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63087

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63026

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54092

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52170