XC2S50-5TQG144I FPGA:機能、仕様、アプリケーション、プログラミングガイド

XC2S50-5TQG144Iは、AMD XilinxのSpartan-IIファミリーの柔軟で強力なFPGA(フィールドプログラム可能なゲートアレイ)です。カスタマイズ、速度、信頼性を必要とするデジタルプロジェクト向けに設計されています。このガイドでは、このFPGAの機能、仕様、プログラミングプロセス、および使用について説明して、その最大限のものを理解するのに役立ちます。カタログ

XC2S50-5TQG144Iの概要

XC2S50-5TQG144I AMD XilinxのSpartan-II FPGAであり、柔軟性とパフォーマンスを必要とするデジタルプロジェクト向けに設計されています。50,000個のシステムゲートと1,728個のロジックセルがあり、複雑なタスクを処理できます。チップには、384の構成可能なロジックブロック(CLB)と32,768のRAMビットが含まれており、優れたメモリと処理能力が与えられます。92の入力/出力(I/O)ピンを使用すると、他のコンポーネントに簡単に接続できます。コンパクトで使いやすい144ピンの薄いクアッドフラットパック(TQFP)があります。FPGAは2.5V(2.375Vから2.625Vの安全な範囲)で動作し、-40°Cから +100°Cの温度でうまく機能します。このSpartan-II FPGAは0.18ミクロンのテクノロジーで作られており、効率的で信頼性が高くなっています。プログラム可能です。つまり、必要に応じてその機能を更新できます。

費用対効果の高い高性能ソリューションの場合、私たちと一緒にバルクオーダーを配置することが最適な選択であり、優れた品質を確保します。

XC2S50-5TQG144I CADモデル

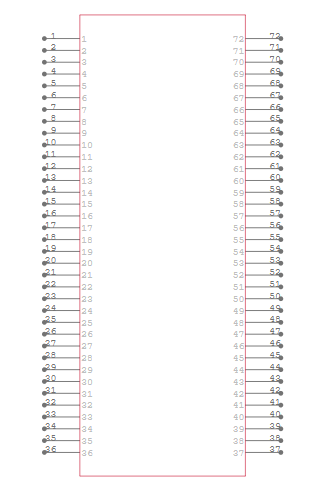

XC2S50-5TQG144Iシンボル

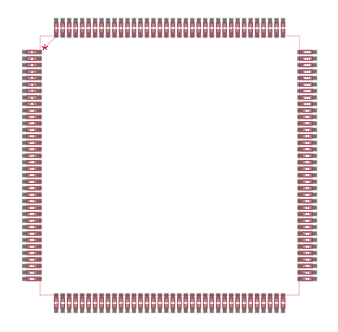

XC2S50-5TQG144Iフットプリント

XC2S50-5TQG144I 3Dモデル

XC2S50-5TQG144I機能

• システムゲート:XC2S50-5TQG144I FPGAは、約50,000のシステムゲートを提供しています。これにより、かなりの量のロジック処理機能を必要とする複雑なデジタル設計とアプリケーションをサポートできます。

• 論理セル:このデバイスには、複雑なロジック構成の実装を容易にし、FPGA内のさまざまなデジタル機能の作成を促進する1,728個のロジックセルが含まれています。

• 構成可能なロジックブロック(CLB):FPGAのロジックの基盤を提供する384の構成可能なロジックブロック(CLB)を備えています。これらのブロックは、特定の設計要件を満たすようにプログラムおよび再構成し、デバイスの全体的な汎用性を高めることができます。

• ラム:FPGAには32,768ビットの内部RAMが装備されており、データ操作と一時的なデータストレージを含むタスクの効率的なデータストレージと検索機能を提供します。

• I/Oピン:92 I/Oピンを使用すると、XC2S50-5TQG144Iは十分な外部接続を保証し、包括的なシステム統合のためのシステム内の他のデバイスやコンポーネントとインターフェイスできるようにします。

• 動作電圧:デバイスは、2.375Vから2.625Vの許容範囲の公称電圧2.5Vで動作します。この電圧範囲は、さまざまな電気条件下で安定した動作と信頼性の高いパフォーマンスを確保するのに役立ちます。

• 温度範囲:XC2S50-5TQG144Iは、-40°Cから +100°Cまでの広い温度範囲で効果的に動作するように設計されており、熱条件が困難な環境での展開に適しています。

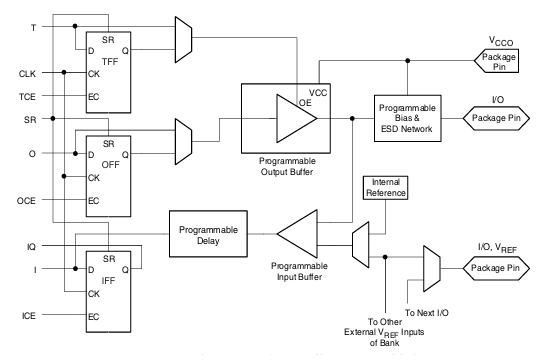

XC2S50-5TQG144Iブロック図

図は、信号がどのように移動するかを示しています XC2S50-5TQG144I FPGA。チップが入力信号と出力信号を処理して他のコンポーネントと通信する方法を説明します。に 出力側 、信号はFPGA内から来て、Flip-Flopsと呼ばれるストレージユニットを通過します。これらのフリップフロップはデータを保持し、信号が適切なタイミングで変更されるようにします。その後、信号はプログラム可能な出力バッファーを通過します。これにより、信号の強度が調整され、変化の速さが制御されます。また、出力がアクティブであるかオフにするかを決定するスイッチ(OEコントロール)もあります。保護回路は、信号が他のデバイスに接続するI/Oピンに到達する前に、静電気の損傷を防ぎます。に 入力側、外部からの信号は、プログラム可能な入力バッファーを介して入ります。これは、FPGA内に送信する前にそれらを処理します。プログラム可能な遅延ユニットは、信号のタイミングを調整するのに役立ち、すべてが同期し続けるようにします。FPGAは、内部参照電圧(VREF)を使用して異なる電圧レベルを一致させることもでき、さまざまなタイプの回路での作業を容易にすることもできます。一部のI/Oピンは、この電圧参照を共有して、信号を安定させます。この設計は、FPGAが信号を効率的に管理し、異なる電子コンポーネントとの適切なタイミング、保護、互換性を確保するのに役立ちます。

XC2S50-5TQG144I仕様

|

タイプ |

パラメーター |

|

メーカー |

amd xilinx |

|

シリーズ |

Spartan®-II |

|

パッケージング |

トレイ |

|

パーツステータス |

廃止 |

|

ラボ/CLBの数 |

384 |

|

ロジック要素/セルの数 |

1728 |

|

合計RAMビット |

32,768 |

|

I/Oの数 |

92 |

|

ゲートの数 |

50,000 |

|

電圧 - 供給 |

2.375V〜2.625V |

|

取り付けタイプ |

表面マウント |

|

動作温度 |

-40°C〜100°C(TJ) |

|

パッケージ /ケース |

144-LQFP |

|

サプライヤーデバイスパッケージ |

144-TQFP(20x20) |

|

基本製品番号 |

XC2S50 |

XC2S50-5TQG144Iアプリケーション

組み込みシステム

組み込みシステムでは、XC2S50-5TQG144Iは、マイクロコントローラーベースのアプリケーションに必要なロジックを提供します。機能性と応答性を高めるために、自動車電子機器、ポータブルデバイス、および小規模ロボット工学で広く使用されています。

信号処理

FPGAは、並列処理を実行する能力が必要な信号処理タスクに優れています。オーディオおよびビデオ処理、通信、およびデータ分析に最適であり、複雑なアルゴリズムと高速データストリームを処理するための馬力を提供します。

産業制御システム

産業制御システムは、このFPGAの堅牢性とプログラマ性の恩恵を受けており、プロセス制御、機械の自動化、システム監視などのアプリケーションに適しています。その信頼性は、精度と運用の安定性を必要とする環境で一貫したパフォーマンスを保証します。

通信システム

通信システムでは、XC2S50-5TQG144Iは、データの送信と受信、信号変調や復調、プロトコル変換、ネットワークルーティングなどのアクティビティのサポートを管理するのに役立ちます。その適応性は、進化する通信インフラストラクチャと新興のワイヤレステクノロジーにおいて重要です。

プロトタイピングと開発

FPGAは、デジタルサーキットのプロトタイピングにも広く使用されています。多くの人は、特に複雑なASICおよびカスタムチップ設計プロジェクトで、最終制作の前にアイデアをテストおよび改良するためにそれを利用しています。この機能により、開発時間とコストが削減され、コンセプトから市場へのパスが加速されます。

XC2S50-5TQG144I同様の部分

XC2S50-5TQG144I利点

費用対効果

XC2S50-5TQG144Iは、その手頃な価格で際立っており、多くの競合するFPGAよりも1ドルあたりの機能を提供します。この費用対効果は、高度なプロセステクノロジーと効率的なアーキテクチャを通じて達成され、費用に敏感な市場でのより広範な展開を可能にします。

高性能I/Oおよびパッケージ

このFPGAは、幅広いI/O標準をサポートしており、さまざまな費用対効果の高いパッケージングオプションで利用できます。これらの機能により、パフォーマンスを犠牲にすることなくデバイスを複数のアプリケーションに統合できるようになり、インターフェイスのバラサイティ性と物理的制約が要因であるハイエンドおよびボリューム駆動型市場の両方に理想的になります。

システムレベルの機能

分散RAMや構成可能なブロックRAMなどの高度なメモリ管理機能を備えたXC2S50-5TQG144Iは、データ処理効率を高めます。これらの機能により、複雑なデータストレージと処理タスクが容易になり、システムの全体的なパフォーマンスとスケーラビリティが向上します。

再プログラム可能性

XC2S50-5TQG144Iの再プログラム可能性により、その構成を無制限に変更できます。これは、開発フェーズ中に有益です。この柔軟性により、ハードウェアコストを追加せずに、反復的な更新を介してデザインを改良し、イノベーションを促進し、最終製品までの時間を短縮できます。

XC2S50-5TQG144Iプログラミング手順

AMD XilinxのSpartan-IIシリーズのXC2S50-5TQG144I FPGAのプログラミングには、デジタル設計を機能的なFPGA構成に効率的に変換するように設計された構造化された一連のステップが含まれます。これは、プログラミングプロセスを通じてお手伝いできる統合された詳細なガイドです。

1.設計エントリ

VHDLやVerilogなどのハードウェア説明言語(HDL)を使用してデジタルロジックを作成するデザインエントリフェーズから始めます。この最初のステップでは、FPGAに実装する機能とロジックの詳細を詳しく説明します。設計は正確であり、合成と実装を成功させるために意図した操作を正確に表す必要があります。

2.合成

合成ステップでは、合成ツールを使用してHDLコードをネットリストに変換します。ネットリストは、ゲートやフリップフロップなどのさまざまな相互接続された論理要素を含む形式へのデザインの内訳です。このプロセスは、FPGAが理解して実装できる実用的な青写真に、理論的設計を実用的な青写真に変換します。

3.実装

実装には、マッピング、配置、ルーティングのいくつかのサブステップが含まれます。マッピングは、ネットリストの要素をFPGA内の特定のロジックブロックに割り当てます。配置すると、FPGAチップ上のこれらのブロックの物理的な位置が決定され、パフォーマンスとリソースの使用率が最適化されます。ルーティングは、FPGAのプログラム可能な相互接続リソースを介してこれらのブロックを接続します。このフェーズにより、設計がすべての物理的およびパフォーマンスの制約を満たすことが保証されます。

4.制約定義

設計プロセス中に、制約の定義が必要です。制約は、タイミング(FPGAの動作速度)やピンの割り当て(FPGAのピンがハードウェアのさまざまな部分に接続する)などの要件を指定することにより、実装ツールをガイドします。これらはユーザー制約ファイル(UCF)に明確にされており、特定の運用基準を満たすために設計を微調整するのに役立ちます。

5.ビットストリーム生成

デザインが実装フェーズを正常に通過したら、次のステップはビットストリームファイルを生成することです。このファイルには、FPGAがデザインを実行するために必要なすべての構成データが含まれています。BitStreamはプログラミングプロセスの最終出力であり、FPGAの完全なプログラムされた状態を表しています。

6.デバイスプログラミング

最後のステップは、ビットストリームをXC2S50-5TQG144I FPGAにロードすることです。これは、セットアップに応じてさまざまな構成モードを使用して実行できます。で マスターシリアルモード、FPGAは、添付されたシリアルPROM(プログラム可能な読み取り専用メモリ)から構成データを自律的に読み取ります。 スレーブシリアルモード マイクロコントローラーなどの外部マスターデバイスがFPGA構成データにシリアルにフィードすることができます。 スレーブパラレルモード 外部マスターデバイスから構成データを並行して提供することにより、高速プログラミングを有効にします。最後に、 境界スキャン(JTAG)モード プログラミングとテストの両方にJTAGインターフェイスを利用しているため、開発中に反復デバッグと検証のために役立ちます。

XC2S50-5TQG144Iパッケージングの寸法

XC2S50-5TQG144I XilinxのSpartan-IIファミリーからのフィールドプログラム可能なゲートアレイ(FPGA)であり、 144ピン薄Quadフラットパック(TQFP)パッケージ。このパッケージは測定します 20 mm x 20 mm。

XC2S50-5TQG144Iメーカー

XC2S50-5TQG144Iは、AMD Xilinxが製造したSpartan-IIファミリーのFPGAです。Xilinx、今の一部 AMD、FPGA、適応SOC、およびその他のプログラム可能なロジックデバイスを専門とする大手半導体会社です。XC2S50-5TQG144Iは、もともとXilinx Spartan-IIシリーズの下で開発され、50,000個のシステムゲートと1,728個の論理セルを提供し、高性能でありながら費用対効果の高いアプリケーション用に設計されています。AMDによるXilinxの買収により、同社はSpartan-IIシリーズのようなレガシー製品を引き続きサポートし、新しいFPGAアーキテクチャを進めています。ただし、XC2S50-5TQG144Iは古い世代のFPGAであり、AMD Xilinxがより高度なFPGAファミリーに焦点を移すと、最終的な陳腐化に直面する可能性があります。

結論

XC2S50-5TQG144I FPGAは、優れたパフォーマンスと柔軟性を提供する費用対効果の高い再プログラム可能なチップです。これは、高速処理と強力な接続オプションのため、組み込みシステム、産業機械、通信ネットワークで広く使用されています。このFPGAは、プログラムおよび更新を行う能力により、最終制作前に新しいアイデアをテストおよび開発するのに役立ちます。新しいFPGAは利用可能ですが、このモデルは、信頼できる手頃な価格のFPGAソリューションを必要とするプロジェクトのための確固たる選択肢のままです。このガイドは、FPGAの機能、用途、プログラミングプロセスの明確で簡単な概要を提供し、すべての人にとって貴重なリソースになります。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1.高速アプリケーションにXC2S50-5TQG144Iを使用できますか?

XC2S50-5TQG144Iは、最大200 MHzの速度をサポートしているため、ほとんどの組み込みおよび産業用途に適しています。ただし、プロジェクトにPCIEやDDRメモリなどの高速インターフェイスが必要な場合は、Spartan-6やArtix-7シリーズなどのより高度なFPGAが必要になる場合があります。

2。XC2S50-5TQG144Iは、新しいSpartan-3またはSpartan-6 FPGASとどのように比較されますか?

Spartan-3やSpartan-6などの新しいFPGAは、パフォーマンス、より高い論理密度、および追加機能を提供しますが、XC2S50-5TQG144Iは、中程度の複雑さを持つ高感受性プロジェクトには好ましい選択肢です。レガシーの互換性または安定したサプライチェーンが必要な場合、XC2S50-5TQG144Iは素晴らしい選択肢です。

3. XC2S50-5TQG144I FPGAと互換性のあるプログラミングツールは何ですか?

XC2S50-5TQG144Iは、Xilinx ISE(統合ソフトウェア環境)を使用してプログラムされています。Vivadoなどの新しいXilinxツールはSpartan-IIファミリーをサポートしていませんが、ISEはこのFPGAに必要なすべての設計、合成、およびプログラミング機能を提供します。

4.既存のSpartan-IIデザインを新しいFPGAに移行できますか?

はい、ただし、変更が必要です。新しいSpartan-3およびSpartan-6ファミリは、さまざまなアーキテクチャ、電圧レベル、および構成方法を使用しています。移行を検討している場合は、適切な代替案を選択し、設計の変更を最小限に抑えるのを支援できます。

5。XC2S50-5TQG144IはJTAGプログラミングをサポートしていますか?

A:はい、FPGAはJTAG(IEEE 1149.1)境界スキャンプログラミングをサポートしています。これにより、標準のJTAGインターフェイスを使用して簡単なデバッグと構成が可能になります。これは、外部メモリなしの初期プログラミングと再構成の両方に役立ちます。

XC4013XL-3PQ240C FPGA:代替、仕様、アプリケーション、およびデータシート

03/18/2025で公開されています

RFパワーアンプ:どのように機能するか、どのタイプがより効率的ですか

03/18/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/16/8000で公開されています 147710

-

USB-Cピンアウトと機能

04/16/2000で公開されています 111644

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/16/1600で公開されています 111313

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/16/0400で公開されています 83571

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79202

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66734

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 62920

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 62784

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54018

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 51931