XC4VLX100-10FFG1148C FPGA: 機能、仕様、アプリケーション、およびプログラミング ガイド

複雑なデジタル設計を扱う場合、XC4VLX100-10FFG1148C は必要なパワーと柔軟性を提供します。この FPGA は、高い論理容量、内蔵メモリ、多数の I/O ピンを備えているため、要求の厳しいアプリケーションに最適です。このガイドでは、その機能、パフォーマンス、タイミング パラメーター、アプリケーション、プログラミング手順、長所と短所、パッケージの詳細、メーカーの背景について学びます。カタログ

XC4VLX100-10FFG1148Cとは何ですか?

の XC4VLX100-10FFG1148C は、Xilinx (現 AMD) の高性能 FPGA であり、90 nm 銅プロセスで構築された Virtex-4 LX ファミリに属しています。このデバイスは、複雑なデジタル ロジックの実装向けに設計されており、高速シリアル トランシーバーを使用せずにロジックとメモリ リソースを重視する LX シリーズの一部です。1148 ボール FCBGA パッケージと商用温度定格によって識別され、LX ラインナップ内の高容量オプションの 1 つを表します。

XC4VLX100-10FFG1148Cをお探しですか?現在の在庫、納期、価格を確認するにはお問い合わせください。

XC4VLX100-10FFG1148Cの特長

• 高いロジック容量

XC4VLX100-10FFG1148C は 110,592 個のロジック セルを提供し、単一デバイス上で複雑なデジタル設計を実装できます。この大きな論理容量により、高密度の処理および制御機能に適しています。

• 組み込みおよび分散メモリ

ブロック RAM と分散 RAM を組み合わせた合計約 4.22 M ビットのメモリが統合されています。このメモリ アーキテクチャは、大規模な外部メモリを必要とせずに、効率的なデータ ストレージ、バッファリング、およびオンチップ処理をサポートします。

• 豊富な I/O リソース

このデバイスは 768 個のユーザー I/O ピンを提供し、さまざまな外部コンポーネントやシステムとのインターフェイスに柔軟性を与えます。これらの I/O は、SelectIO™ 機能を通じて幅広い標準をサポートし、ボードレベルの接続を強化します。

• 高性能コア

1.2 V のコア電圧で動作する FPGA は、最大約 500 MHz の内部クロックをサポートし、高速なロジック パフォーマンスを実現します。これにより、要求の厳しい高速アプリケーションでも信頼性の高い動作が保証されます。

• 商用温度範囲

このデバイスは 0 °C ~ +85 °C で定格されており、商用グレードの環境向けに設計されています。産業用および組み込みシステムの一般的な動作条件全体で安定したパフォーマンスを維持します。

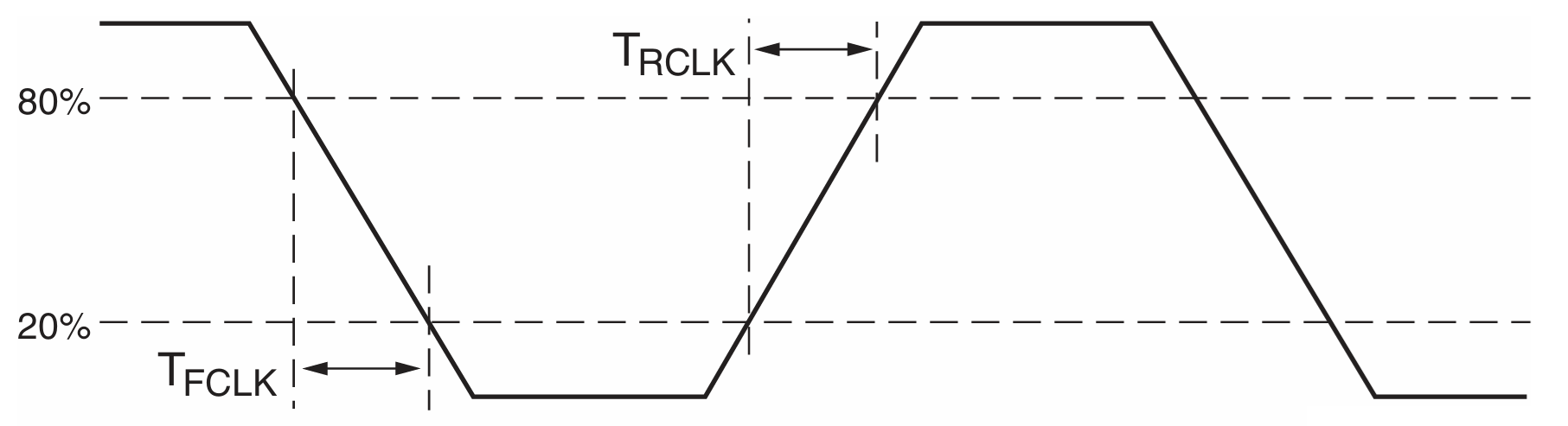

基準クロックのタイミングパラメータ

この図は、T に焦点を当てた、XC4VLX100-10FFG1148C のクロックの立ち上がり時間と立ち下がり時間の測定を示しています。RCLK (立ち上がり時間) と TFCLK (立ち下がり時間) クロック信号の 20% と 80% の電圧レベルの間。これは、クロックが Low から High、および High から Low にどれだけ早く遷移するかを示しており、FPGA のタイミングの完全性と信頼性の高い動作を維持するのに役立ちます。これらのエッジを正確に制御することで、内部ロジックと外部インターフェイスの正確な同期が保証されます。XC4VLX100-10FFG1148C では、安定した高速性能と信号歪みを最小限に抑えるために、適切な立ち上がり時間と立ち下がり時間を維持することが重要です。

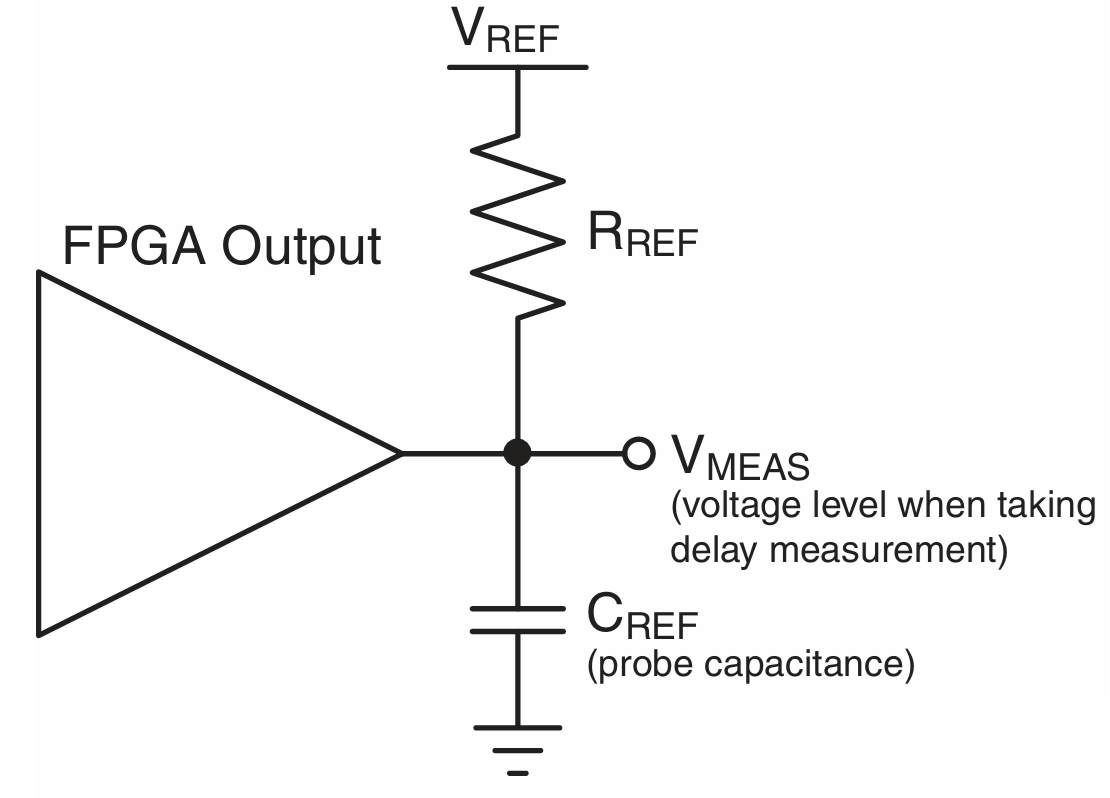

一般化されたテストのセットアップ

この図は、XC4VLX100-10FFG1148C FPGA の出力遅延と信号特性を測定するために使用される一般的なテスト セットアップを示しています。基準抵抗 (R参照) とコンデンサ (C参照) は FPGA 出力に接続されており、V測定 タイミング測定が行われる電圧レベルを表します。この標準化されたセットアップにより、さまざまなテスト環境にわたる信号遷移遅延の一貫した正確な測定が保証されます。XC4VLX100-10FFG1148C の場合、これは高速 I/O パフォーマンスを検証し、デバイスが実際のアプリケーションでタイミング仕様を満たしていることを確認するために重要です。

XC4VLX100-10FFG1148Cの仕様

|

タイプ |

パラメータ |

|

メーカー |

AMD/ザイリンクス |

|

シリーズ |

Virtex®-4 LX |

|

包装 |

トレイ |

|

部品のステータス |

アクティブ |

|

LAB/CLB の数 |

12288 |

|

ロジックエレメント/セルの数 |

110592 |

|

合計RAMビット数 |

4423680 |

|

I/O数 |

768 |

|

電圧 – 電源 |

1.14V~1.26V |

|

取付タイプ |

表面実装 |

|

動作温度 |

0℃~85℃(TJ) |

|

パッケージ・ケース |

1148-BBGA、FCBGA |

|

サプライヤーデバイスパッケージ |

1148-FCPBGA(35×35) |

|

基本製品番号 |

XC4VLX100 |

XC4VLX100-10FFG1148C アプリケーション

1. デジタル信号処理 (DSP) システム

XC4VLX100-10FFG1148C は、大規模なロジック容量と組み込みメモリにより、高性能 DSP アルゴリズムの実装に最適です。集中的な計算を時間内に処理するカスタム処理パイプラインを構築できます。このため、画像処理、レーダー システム、高度なフィルタリングなどのアプリケーションに最適です。

2. 組み込みシステムの高速化

このデバイスは、柔軟なアーキテクチャにより、プロトコル処理、バス管理、ハードウェアのオフロードなどの組み込みシステム機能を高速化するために広く使用されています。タスクをソフトウェアから FPGA ファブリックに移行することで、システムの応答性が向上します。これにより、設計の柔軟性を維持しながらパフォーマンスを最適化することができます。

3. 通信およびネットワーク機器

FPGA は I/O 数と処理能力が高いため、スイッチ、ルーター、インターフェイス ブリッジなどの通信インフラストラクチャに適しています。複雑なネットワーク プロトコルと高帯域幅のデータ ストリームを低遅延で管理できます。これにより、バックボーン ネットワーキングやデータセンター システムにとって信頼できる選択肢となります。

4. 高速なデータ取得と処理

XC4VLX100-10FFG1148C は、計測機器や科学機器など、迅速なデータのキャプチャと処理を必要とするアプリケーションに優れています。内蔵メモリとロジック リソースにより、高速バッファリングと並列データ操作が可能になります。これにより、環境内で大量のデータを効率的に処理できるようになります。

XC4VLX100-10FFG1148C 類似部品

|

仕様 |

XC4VLX100-10FFG1148C |

XC4VLX100-10FFG1148I |

XC4VLX100-11FFG1148C |

XC4VLX100-10FF1148C |

XC4VLX100-10FFG1513C |

XC4VLX100-12FFG1148C |

|

メーカー |

ザイリンクス (AMD) |

ザイリンクス (AMD) |

ザイリンクス (AMD) |

ザイリンクス (AMD) |

ザイリンクス (AMD) |

ザイリンクス (AMD) |

|

家族 |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

|

ロジック容量 |

110,592 セル |

110,592 セル |

110,592 セル |

110,592 セル |

110,592 セル |

110,592 セル |

|

パッケージの種類 |

FCBGA |

FCBGA |

FCBGA |

FCBGA |

FCBGA |

FCBGA |

|

ボール数 |

1148 |

1148 |

1148 |

1148 |

1513 |

1148 |

|

スピードグレード |

–10 |

–10 |

–11 |

–10 |

–10 |

–12 |

|

温度グレード |

コマーシャル(C) |

工業用(I) |

コマーシャル(C) |

コマーシャル(C) |

コマーシャル(C) |

コマーシャル(C) |

|

コア電圧 |

1.2V |

1.2V |

1.2V |

1.2V |

1.2V |

1.2V |

|

動作温度範囲 |

0℃~+85℃ |

-40 °C ~ +100 °C |

0℃~+85℃ |

0℃~+85℃ |

0℃~+85℃ |

0℃~+85℃ |

|

違い |

ベースパーツ、標準パッケージ |

工業用温度サポート |

より高速なグレード |

「G」指定がない |

パッケージが大きくなり、I/O が増加 |

シリーズ最速のスピードグレード |

XC4VLX100-10FFG1148C プログラミング手順

XC4VLX100-10FFG1148C をプログラミングする前に、開発環境と構成ファイルが適切に設定されていることを確認する必要があります。このデバイスは複数の構成モードをサポートしているため、適切な構成モードを早期に選択することで、プログラミング プロセスをスムーズかつ成功させることができます。

1. デバイスの電源を入れる

まず、必要な電圧レール (VCCINT、VCCAUX、および VCC_CONFIG) を使用して FPGA に電力を供給します。構成を開始する前に、これらの電圧が安定したレベルに達していることを確認する必要があります。初期化エラーを避けるためには、適切な電源シーケンスが有効です。

2. 構成モードを選択します

次に、FPGA は INIT_B の立ち上がりエッジで MODE ピンをサンプリングし、使用するコンフィギュレーション方法を決定します。セットアップに応じて、JTAG、スレーブ シリアル、マスター シリアル、または SelectMAP から選択できます。モード ピンはビットストリームのロード方法を制御するため、モード ピンが正しく設定されていることを確認してください。

3. デバイスの初期化

FPGA は初期化中にコンフィギュレーション メモリをクリアし、ビットストリームのロードの準備をします。この段階では、INIT_B、GWE、GTS などの信号を使用してデバイスを既知の状態に設定します。続行する前に、すべての初期化信号が期待どおりに動作することを確認する必要があります。

4. ビットストリームをロードする

選択したインターフェイスを使用して、コンフィギュレーション ビットストリームを FPGA にストリーミングします。たとえば、JTAG を使用する場合、ビットストリームはデバイスのコンフィギュレーション メモリにシリアルにシフトされます。プログラミングを成功させるには、正確かつ完全なビットストリーム転送が必要です。

5. 構成プロセスの開始

ビットストリームが完全にロードされると、FPGA はシフト モードを終了し、起動シーケンスを開始します。JSTART コマンドまたは同等のプロセスにより、デバイスが設定を完了するようにトリガーされます。FPGA が中断せずにこのステージを完了できるようにする必要があります。

6. 設定を完了し、ユーザーモードに入る

FPGA は CRC を使用してビットストリームの整合性を自動的にチェックし、有効な場合は DONE 信号をアサートします。これが発生すると、ユーザー ロジックがアクティブになり、デバイスは設計に従って動作します。この時点で、コンフィギュレーション プロセスは完了し、FPGA は完全に機能するようになります。

7. オプションの検証

最後に、リードバックまたは検証手順を実行して、構成が成功したことを確認できます。これは、使用したモードに応じて、JTAG または SelectMAP を通じて実行できます。オプションではありますが、システムが適切なプログラミングを確認するために、これを強く推奨します。

XC4VLX100-10FFG1148C の長所と短所

利点

• 多くの 90 nm FPGA と比較して全体の消費電力が低い。

• 成熟した安定した設計エコシステムによってサポートされています。

• 同世代としては優れたパフォーマンス対コスト比。

• モジュール式 ASMBL アーキテクチャにより、設計効率が向上します。

• 長年確立された設計のための信頼性と実績のあるプラットフォーム。

短所

• 将来のサポートが限定されている従来のテクノロジーに基づいています。

• 新しいファミリに搭載されている高速シリアル トランシーバがありません。

• 最新の FPGA と比較して、スケーラビリティと柔軟性が低い。

• 製品の古さによる潜在的な調達問題。

• 使用率が高い場合は、慎重な電力および温度管理が必要です。

XC4VLX100-10FFG1148C 梱包寸法

|

パラメータ |

寸法 |

|

パッケージの種類 |

FFG1148 (フリップチップファインピッチ BGA) |

|

ボールピッチ |

1.00mm |

|

パッケージ本体サイズ(縦×横) |

35.00mm×35.00mm |

|

パッケージ本体サイズ (長さ×幅、インチ) |

1.378インチ×1.378インチ |

|

パッケージ全体の高さ (A) |

3.40 mm (標準) |

|

パッケージ全体の高さ (A、インチ) |

0.134 インチ (標準) |

|

ボディサイズ許容差 |

±0.20mm |

|

ボールアレイ |

34×34(1.00mmピッチグリッド) |

|

ボール数 |

1,148球 |

|

ボール径(呼び) |

0.60mm |

|

基板厚さ(B) |

~1.00mm |

|

スタンドオフ高さ (A1) |

0.40mm(公称) |

|

ヒートスラグ・メタルキャップサイズ |

~32 mm 四方 (一般的な上部金属領域) |

|

取付タイプ |

表面実装 |

XC4VLX100-10FFG1148C メーカー

XC4VLX100-10FFG1148C は、 ザイリンクス、プログラマブル ロジック デバイスの分野のパイオニアです。2022 年にザイリンクスは AMD (Advanced Micro Devices) を獲得し、ハイパフォーマンス コンピューティングと適応テクノロジーにおける地位をさらに強化します。この合併により、ザイリンクスの FPGA 専門知識と AMD の処理リーダーシップが結合され、XC4VLX100-10FFG1148C などの製品に対する堅牢な長期サポートとイノベーションが保証されます。

結論

XC4VLX100-10FFG1148C は、その世代内でその大規模なロジック セル数、柔軟なメモリ アーキテクチャ、幅広い I/O 機能、および堅実なパフォーマンスで際立っています。高速クロッキングと信頼性の高い信号整合性をサポートしているため、DSP、ネットワーキング、組み込みシステムなどの要求の厳しいアプリケーションに最適です。実証済みの安定性と成熟したエコシステムを提供しますが、拡張性と調達に制限があるレガシー テクノロジーを反映しているため、最新の設計には慎重な考慮が重要です。

データシートPDF

XC4VLX100-10FFG1148C データシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1. XC4VLX100-10FFG1148C を新しい FPGA ファミリと比較するとどうですか?

Virtex-6、7 シリーズ、UltraScale などの新しいファミリは、高速、低消費電力、統合シリアル トランシーバを提供します。ただし、XC4VLX100-10FFG1148C は、最新の機能を必要としない安定したレガシー システムに優れた価値を提供します。

2. XC4VLX100-10FFG1148C と互換性のある開発ツールは何ですか?

ザイリンクス ISE Design Suite を使用して、合成、インプリメンテーション、ビットストリーム生成を行うことができます。これは古い FPGA ファミリであるため、Vivado などの新しいツールはサポートしていないため、互換性のある開発環境があることを確認してください。

3. XC4VLX100-10FFG1148C は温度に敏感な環境でも使用できますか?

このデバイスは、0 °C ~ +85 °C の商用温度範囲で定格されており、ほとんどの標準的な産業および組み込み条件に適しています。より過酷な環境では、温度範囲が拡張されたバージョンが必要になる場合があります。

4. XC4VLX100-10FFG1148C は高速データ処理アプリケーションに使用できますか?

はい。500MHzの内部クロックと大容量ロジックにより、高速信号処理を効率よく処理します。ただし、パフォーマンスを最大化するには、適切なタイミング制約とボードレベルのレイアウトを設計する必要があります。

5. XC4VLX100-10FFG1148C には特別な冷却または温度管理が必要ですか?

使用率が高い場合、この FPGA はかなりの熱を発生する可能性があります。パフォーマンスを維持し、スロットルや長期的な損傷を回避するには、適切なエアフロー、ヒートシンク、またはボードレベルの熱設計を提供する必要があります。

BCM5221KPB イーサネット PHY: 機能、ブロック図、アプリケーション、データシート

10/12/2025で公開されています

電源回路を保護するために速断ヒューズと遅断ヒューズを選択する方法

10/11/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/18/8000で公開されています 147772

-

USB-Cピンアウトと機能

04/18/2000で公開されています 112010

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/18/1600で公開されています 111351

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/18/0400で公開されています 83769

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79565

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66960

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63100

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63040

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54097

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52184