EPM7256AETC144-10N CPLD:データシート、仕様、アプリケーション、およびプログラミングガイド

EPM7256AETC144-10Nは、IntelのMAX®7000Aシリーズのプログラマブルロジックデバイス(CPLD)です。このチップは、10 ns遅延で最大172.4 MHzで実行される高速性能のために設計されています。このガイドでは、機能、仕様、用途、プログラム方法、ピンレイアウトなど、このCPLDに関するすべてを説明しています。デジタルサーキット用の信頼できるプログラム可能なチップが必要な場合、この記事はそれがどのように機能するかを理解するのに役立ちます。カタログ

EPM7256AETC144-10N説明

EPM7256AETC144-10N IntelのMAX®7000Aシリーズの高性能CPLDで、ロジック統合タスクの要求に合わせて調整されています。このデバイスには、256個のマクロセルと約5,000個の使用可能なゲートがあり、複雑なデジタル環境で実質的な設計の柔軟性と効用を促進します。わずか5.5 nsの伝播遅延で172.4 MHzの最大周波数で動作すると、迅速な動作のために設計されています。3.3Vの動作電圧で設計され、コンパクトな144ピンの薄いクアッドフラットパック(TQFP)にパッケージ化されたEPM7256AETC144-10Nは、堅牢なロジック設計要件をサポートしています。EPM7256AETC144-10Nは、EEPROMベースの非揮発性構成メモリを使用して、プログラミングデータの永続的な保存を可能にします。この機能は、JTAGインターフェイスを介したシステム内プログラマ性と組み合わせて、更新とフィールドの再プログラミングを容易にし、物理的な再構成や交換を必要とせずに長期的な使いやすさを向上させます。

EPM7256AETC144-10Nのバルク注文を今日私たちに配置し、確実なCPLDソリューションを確保することにより、信頼できるフィールドで実証されたテクノロジーでプロジェクトを保護します。

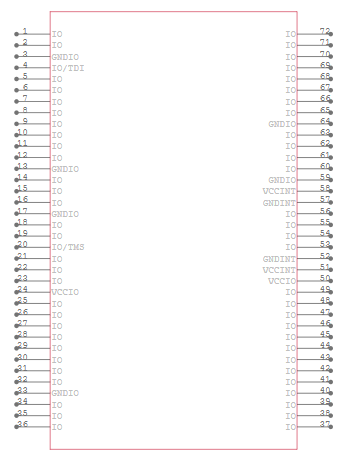

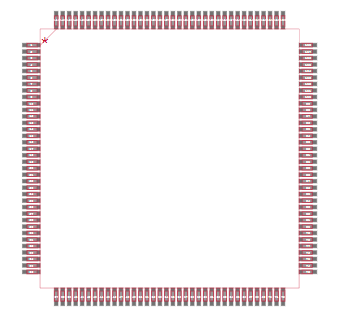

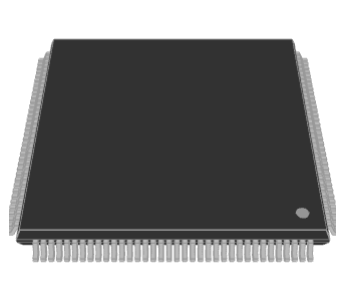

EPM7256AETC144-10N CADモデル

EPM7256AETC144-10Nシンボル

EPM7256AETC144-10Nフットプリント

EPM7256AETC144-10N 3Dモデル

EPM7256AETC144-10N機能

マクロセル:このデバイスには256個のマクロセルが装備されています。マクロセルは、CPLDがさまざまなロジック関数を実行できるようにする構成可能なロジックコンポーネントです。

使用可能なゲート:約5,000の使用可能なゲートを提供します。これは、デバイス内で構成できる基本的なロジックゲート(同様、またはそうではない)を指します。

I/Oピン:CPLDには、120個の入出力ピンがあり、ユーザーの電子設計の他の部分との広範なインターフェースを可能にします。

伝播遅延(TPD):最大伝播遅延は10ナノ秒で、CPLDが入力信号を処理して出力を生成できる速さを決定します。

動作周波数:最大95.2 MHzの周波数で動作できます。これは、デバイスがロジック操作を実行できる速度を定義します。

供給電圧:デバイスは、3.3Vの供給電圧で動作し、一般的な低電圧デジタルロジックレベルで整列しています。

パッケージ:144ピンの薄いクアッドフラットパック(TQFP)に入っています。これは、印刷回路基板に必要なスペースを最小限に抑えるために有利なコンパクトなパッケージタイプです。

動作温度範囲:動作温度範囲は0°Cから70°Cのものであり、広範囲の環境条件で信頼できるパフォーマンスを確保しています。

システム内のプログラマ性:CPLDは、IEEE STDを介してシステム内のプログラム性をサポートしています。1149.1ジョイントテストアクショングループ(JTAG)インターフェイス。最終的なハードウェア構成内でロジックデバイスのプログラミングと再プログラミングを可能にします。

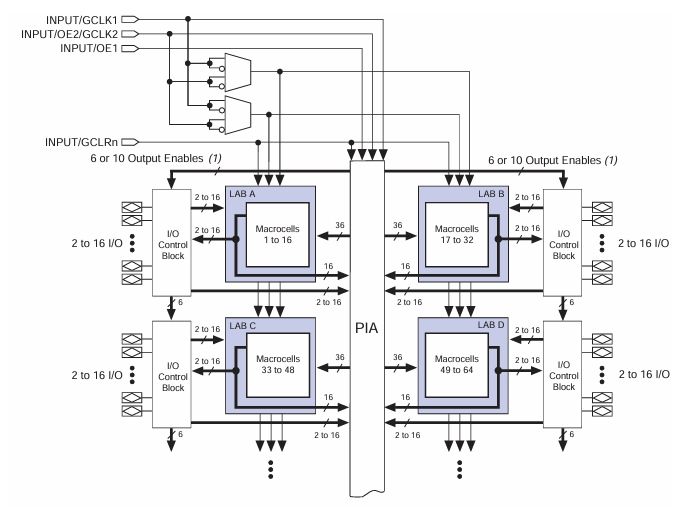

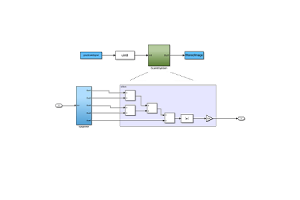

EPM7256AETC144-10Nブロック図

EPM7256AETC144-10N aです 複雑なプログラム可能なロジックデバイス(CPLD) 4で ロジックアレイブロック(ラボ) 、それぞれ16個のマクロセルを含み、合計64個のマクロセル。これらのマクロセルは、組み合わせロジックとシーケンシャルロジックの両方を処理し、さまざまなデジタルロジックアプリケーションにデバイスを柔軟にします。CPLDの中心にあります プログラム可能な相互接続配列(PIA)、すべてのラボを接続し、効率的な信号ルーティングを確保します。各ラボは、36の相互接続ラインを使用してPIAと通信し、信号を効率的に共有および処理できるようにします。このデバイスは、各側にI/Oコントロールブロックを備えており、ラボごとに2〜16個のI/Oピンをサポートしています。これらのブロックは、CPLDを外部回路に接続する入力および出力関数の管理に役立ちます。グローバルクロック(GCLK1、GCLK2)、出力を有効にする(OE1)、グローバルリセット(GCLRN)などの制御信号は、デバイス全体のロジック操作を同期させるのに役立ちます。さらに、ロジックゲートは時計とリセットの信号を管理し、スムーズな動作を確保します。このCPLDは、高速ロジック処理用に設計されており、プログラマ性、効率的な信号ルーティング、信頼性の高いI/Oコントロールを提供し、組み込みシステム、通信、産業の自動化に適しています。

EPM7256AETC144-10N仕様

|

タイプ |

パラメーター |

|

メーカー |

アルテラ/インテル |

|

シリーズ |

MAX®7000A |

|

パッケージング |

トレイ |

|

パーツステータス |

廃止 |

|

プログラム可能なタイプ |

プログラム可能なシステムで |

|

遅延時間TPD(1)最大 |

10 ns |

|

電圧供給 - 内部 |

3V〜3.6V |

|

ロジック要素/ブロックの数 |

16 |

|

マクロセルの数 |

256 |

|

ゲートの数 |

5000 |

|

I/Oの数 |

120 |

|

動作温度 |

0°C〜70°C(TA) |

|

取り付けタイプ |

表面マウント |

|

パッケージ /ケース |

144-LQFP |

|

サプライヤーデバイスパッケージ |

144-TQFP(20x20) |

|

基本製品番号 |

EPM7256 |

EPM7256AETC144-10Nアプリケーション

人工知能

このCPLDは、AIハードウェアアクセラレータで採用され、AIアルゴリズムを効率的に処理するために必要な複雑な計算を処理し、AIアプリケーションの速度と信頼性の両方を向上させます。

5Gテクノロジー

5G通信の領域では、EPM7256AETC144-10Nは、信号処理と通信プロトコルの管理に最適です。その高速ロジック操作は、次世代のワイヤレスシステムで必要な迅速な処理を促進します。

クラウドコンピューティング

データセンター内では、このデバイスは処理機能を改善し、大量のデータと複雑な計算を管理するためのコンポーネントとして機能し、クラウドサービスのインフラストラクチャをサポートします。

家電

CPLDは、テレビやゲームコンソールなどの家電製品のアプリケーションを見つけ、デバイスの機能とエクスペリエンスを強化するカスタムロジック関数を実行します。

ワイヤレステクノロジー

これは、シグナルを変調および復調するためにワイヤレス通信デバイスで使用され、ルーターやセルラーモデムなどのデバイスでの効果的かつ効率的な通信を確保します。

産業管理

このデバイスは、機械を制御し、プロセスを管理し、生産性と安全性の向上に貢献する産業用設定の自動化システムに不可欠です。

モノのインターネット(IoT)

IoTデバイスでは、EPM7256AETC144-10Nはデータ処理と通信タスクを管理します。これは、スマートホームや業界の接続されたデバイスのシームレスな操作に最適です。

医療機器

CPLDは、データ収集や信号処理などのタスクに医療機器に適用され、医療診断および治療機器の信頼性と効率性に役割を果たします。

EPM7256AETC144-10N同様の部品

EPM7256AETC144-10N利点

高い論理密度

このデバイスには、256個のマクロセルと約5,000個の使用可能なゲートが詰め込まれているため、単一のチップ内に複雑なロジック回路を実装できます。この高いロジック密度は、より統合されたコンパクトなデザインを促進し、全体的なコンポーネントカウントを削減し、ボードレイアウトを簡素化します。

システム内プログラマ性(ISP)

IEEE STDを介したシステム内のプログラム性を備えています。1149.1 JTAGインターフェイス、EPM7256AETC144-10Nにより、回路内で直接プログラミングして再プログラミングできます。この機能は、迅速なプロトタイピングと反復設計プロセスに非常に貴重であり、チップを交換する必要なく調整を行うことができます。

高速伝播遅延

わずか10 nsの最大伝播遅延により、このCPLDは、高速データ処理とビデオ処理や高周波取引システムなどのタイムリーな応答を必要とするアプリケーションの入力と出力の迅速な処理を保証します。

低消費電力

3.3Vの供給電圧で動作するEPM7256AETC144-10Nは、エネルギー効率のために最適化されています。この低消費電力は、電力管理が運用寿命を延長するのに適しているポータブルおよびバッテリー操作のデバイスで有益です。

包括的なI/O機能

デバイスには120のI/Oピンが装備されており、広範な接続オプションを提供します。これにより、幅広い周辺機器やその他のシステムコンポーネントとの柔軟なインターフェースが可能になり、複雑なマルチデバイス環境に非常に適応可能になります。

不揮発性構成ストレージ

EEPROMベースのメモリのおかげで、CPLDは電源がオフになった後でも構成設定を保持し、パワーサイクル全体でデバイス機能が一貫していることを保証します。この機能は、頻繁な再構成を必要とせずに、信頼できる長期的なパフォーマンスを必要とするアプリケーションに必要です。

EPM7256AETC144-10Nプログラミング手順

EPM7256AETC144-10Nデバイスのプログラミングには、6段階のシステム内プログラミング(ISP)プロセスが含まれます。

1. ISPの入力:この手順により、デバイスの入力部分と出力部分が通常の使用モードからスムーズにプログラミングモードに切り替わるようにします。約1ミリ秒かかります。

2. IDを確認する:プログラミングを開始する前に、デバイスは独自のIDをチェックします。このステップは非常に速いです。

3.バルク消去:これにより、デバイスからの以前のすべてのデータがクリアされます。これは、すべてを消去するコマンドを受け取り、100ミリ秒を待ってすべてが消去されることを確認することでこれを行います。

4.プログラム:これは、新しいデータがデバイスに入れられる場所です。データの各部分について、それはデバイス内の正しいアドレスに送信され、その後、特別なパルスが適切に保存されていることを確認します。

5.検証:プログラミング後、デバイスは、すべてのデータが読み戻し、それを本来のものと比較することにより、すべてのデータが正しく保存されているかどうかをチェックします。

6. EXIT ISP:このステップにより、デバイスをプログラミングモードから通常の使用モードに戻します。また、約1ミリ秒かかります。

プログラミングに必要な合計時間は、各パルスの持続時間と、データの速度の速度と処理するデータの速度の影響を受けます。さまざまなデバイスがプログラムするメモリの量が異なるため、異なる時間がかかる場合があります。

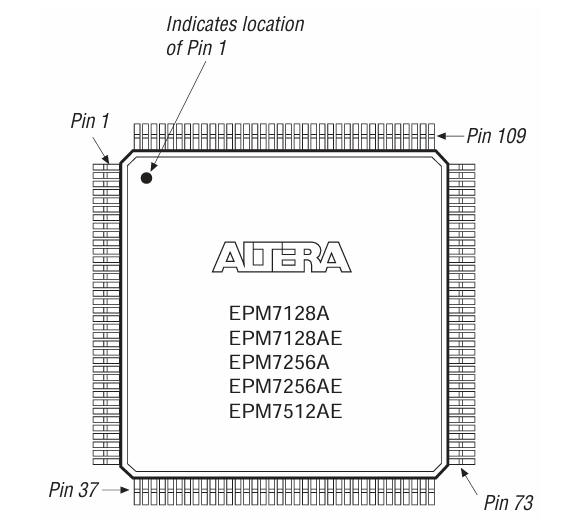

EPM7256AETC144-10Nパッケージピンアウト図

この図は、EPM7256AETC144-10Nパッケージのアウトラインとピン番号を示しています。このチップにはaがあります TQFP-144(144ピン付きの薄いクアッドフラットパッケージ)、つまり、四方すべてにファインピッチのリードがあります。ピン1の位置には小さなドットが付いており、ピン番号はパッケージの周りで反時計回りに増加します。ピン1、ピン37、ピン73、ピン109などのキーリファレンスピンは、PCBアセンブリ中の方向に役立ちます。アウトラインの寸法は、適切なPCBフィッティングを確保するために、チップの物理サイズを定義します。ピンアウト配置により、効率的な信号ルーティングが可能になり、複雑なロジックアプリケーションに適しています。EPM7256AEは、256個のマクロセルとシステム内プログラマ性を備えたMAX 7000A CPLDシリーズの一部です。-10Nサフィックスは、10 ns速度グレードとリードフリーパッケージを示します。

EPM7256AETC144-10Nメーカー

EPM7256AETC144-10Nは、もともとAltera Corporationが開発した複雑なプログラム可能なロジックデバイス(CPLD)であり、後に買収されました。 Intel Corporation 2015年。買収以来、Intelは、このデバイスが属するMAX®7000Aシリーズを含む、AlteraのFPGAおよびCPLD製品ラインの公式メーカーになりました。EPM7256AETC144-10Nは、JTAG(IEEE 1149.1)を介してシステム内プログラム性(ISP)をサポートする高性能で低電力アプリケーション用に設計されています。IntelはAlteraのCPLDテクノロジーを継承しましたが、このデバイスはその後廃止されており、現在は時代遅れに分類されています。

結論

EPM7256AETC144-10Nは、AI、5G、クラウドコンピューティング、工業機械、IoT、および医療機器で使用される強力で柔軟なCPLDです。データを迅速に処理し、ほとんど電力を使用し、回路から削除せずに簡単に再プログラミングできます。安定したパフォーマンスを備えたプログラム可能なロジックを必要とする古いデザインには依然として便利です。このCPLDを使用している場合でも、同様の代替品を探している場合でも、その設計、プログラミング、および利点を理解することで、高速デジタルアプリケーションで最大限に活用することができます。

データシートPDF

EPM7256AETC144-10Nデータシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1. EPM7256AETC144-10Nハンドルは、いくつの論理要素またはゲートがありますか?

EPM7256AETC144-10Nは、256個のマクロセルと約5,000個の使用可能なゲートを提供し、中程度に複雑なロジック実装を可能にします。

2. EPM7256AETC144-10Nをプログラムするにはどうすればよいですか?また、どのツールが必要ですか?

EPM7256AETC144-10Nは、JTAG(IEEE 1149.1)インターフェイスを介してシステム内のプログラム性(ISP)をサポートしています。CHIPに構成データを書き込むために、Altera USB-BlasterまたはIntel Quartus Primeソフトウェアが必要です。

3. EPM7256AETC144-10NとEPM7256AETC144-7の違いは何ですか?

主な違いは速度です。EPM7256AETC144-10Nは10 nsの最大伝播遅延を持ち、EPM7256AETC144-7の高速アプリケーションでは7 ns遅延が速くなります。両方のデバイスは、同じパッケージ、I/Oカウント、およびマクロセル構造を共有しています。

4。EPM7256AETC144-10Nには外部発振器が必要ですか?

いいえ、CPLD自体は外部発振器を必要としませんが、外部クロック入力をサポートします。設計に正確なタイミングが必要な場合は、外部クロック信号を使用してロジック操作を駆動できます。

5. MAX 7000Aシリーズの他のCPLDとEPM7256AETC144-10Nが異なる理由は何ですか?

このCPLDは、高速性能(10 ns伝播遅延)、256のマクロセル、5,000の使用可能なゲートのために際立っているため、複雑な論理設計に最適です。また、一部の古いモデルとは異なり、JTAGを介してシステム内のプログラミング性(ISP)をサポートしています。

MPC8245LZU300Dプロセッサ:データシート、機能、アプリケーション、および仕様

03/13/2025で公開されています

毎日の使用のためのL1154バッテリーの簡単なガイド

03/13/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/19/8000で公開されています 147784

-

USB-Cピンアウトと機能

04/19/2000で公開されています 112078

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/19/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/19/0400で公開されています 83844

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79648

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 67022

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63140

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63071

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54100

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52236