LC5768MC-75F256C CPLD:機能、仕様、利点、アプリケーション

このガイドでは、格子半導体によって作られた小さなが強力なチップであるLC5768MC-75F256Cについて説明します。チップが何をするか、それがどのように機能するか、それをプログラムする方法、そしてそれがどこで使用できるかを示します。ロジックタスクを処理し、低電力を使用し、多くのデバイスで機能するチップを探している場合、このガイドは、LC5768MC-75F256Cが良い選択肢である理由を理解するのに役立ちます。カタログ

LC5768MC-75F256Cとは何ですか?

LC5768MC-75F256C ISPXPLD 5000MCファミリの一部である高性能複合体プログラマブルロジックデバイス(CPLD)です。このデバイスは、1.8Vのコアアーキテクチャを中心に設計されており、768のマクロセルを統合する堅牢なロジック密度を提供します。5000MCシリーズのメンバーとして、信頼できるタイミング制御、効率的なロジック実装、および低電力動作を提供するLatticeの高度なCPLDソリューションを表します。これらはすべて、組み込みおよび高速デジタルシステム用に最適化されています。ISPXPLD 5000MCファミリは、多機能ブロック(MFB)と柔軟なI/Oサポートを導入することにより、従来のCPLDの機能を強化し、LC5768MC-75F256Cをスケーラブルなロジック統合に確実に選択できるようにします。このデバイスは、決定論的なパフォーマンスに合わせて実証済みの信頼性とアーキテクチャを調整し、デジタルデザインの信頼できるビルディングブロックとして機能します。

LC5768MC-75F256Cをお探しですか?現在の在庫、リードタイム、価格を確認するには、お問い合わせください。

LC5768MC-75F256C機能

• 768マクロセル(MFBベースのアーキテクチャ)

このデバイスは、高度な多機能ブロック(MFB)に編成された768のマクロセルを統合し、埋め込み算術およびメモリ機能を備えた高密度ロジックをサポートします。これらのMFBは、ロジック、デュアルポートSRAM、FIFO、およびCAM機能の柔軟な構成を可能にします。

• 1.8Vコア電圧(MCバリアント)

このMCシリーズバリアントは、1.8Vコアで動作し、ポータブルおよび高効率の設計のために低電力消費を提供します。低い電圧にもかかわらず、堅牢な性能と論理密度を維持します。

• 7.5 ns伝播遅延(速度グレード-75)

わずか7.5ナノ秒の最大ピン間伝播遅延を実現し、中程度から高速デジタルアプリケーションに適しています。-75速度グレードは、組み込みシステムの電力と速度のバランスをとります。

• 193プログラム可能なI/Oピン

チップには、複数の電圧標準とプロトコルをサポートする193のI/Oピンが提供されます。これらのピンは完全にプログラム可能であり、他のロジックまたはアナログデバイスとの柔軟なインターフェースを可能にします。

• 超規則的なロジックサポート(ブロックあたり最大136の入力)

各MFBは、最大136の入力信号を持つ非常に広いロジック関数をサポートしており、より少ないロジックレベルで複雑な組み合わせロジックを可能にします。これにより、伝播遅延が減り、論理合成が簡素化されます。

• 組み込みデュアルポートSRAM、FIFO、および三元CAMサポート

MFBは、SRAM(シングル/デュアルポート)、FIFOS、または3成分コンテンツアドレス指定可能なメモリとして機能するように構成できます。この柔軟性により、コンパクトなCPLDでメモリが豊富なロジック設計が可能になります。

• オンチップpll(sysclock™)

組み込みのPLLは、1倍から32倍、位相シフト、および外部フィードバックまでのクロック乗算/除算をサポートします。タイミングを管理し、高速同期システム全体でゆがんでいます。

• ワイドI/O標準サポート(SYSIO™)

I/Oブロックは、LVCMO、LVTTL、SSTL、HSTL、GTL+、LVDS、LVPECLなどの広範なシグナル基準をサポートしています。これにより、単一のデバイスでの混合電圧と微分シグナル伝達が可能になります。

• システム内プログラマ性(ISPXP™)

このデバイスは、IEEE 1532またはSysconfigインターフェイスを通じてシステム内プログラミングをサポートしています。それを削除せずにボードに再プログラムすることができ、設計の更新とフィールド再構成を可能にします。

• 境界スキャンテスト(IEEE 1149.1準拠)

完全なJTAG境界スキャンサポートにより、ボードレベルの堅牢なテストとデバッグが可能になります。これにより、最新のテスト要件へのコンプライアンスが保証され、生産における検証が簡素化されます。

• 5V許容I/O。

1.8Vコアにもかかわらず、I/Oバンクは5V信号を許容し、レガシー電圧インターフェイスをサポートしています。これにより、古いシステムと混合電圧環境との互換性が向上します。

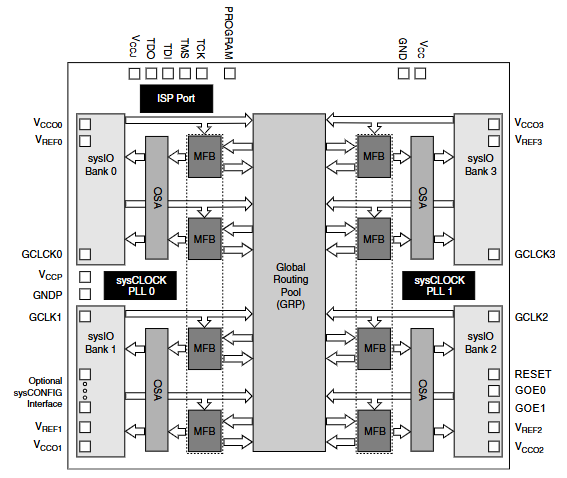

ISPXPLD 5000MX/5000MCブロック図

ISPXPLD 5000MX/5000MCファミリのLC5768MC-75F256Cのブロック図は、プログラム可能なロジックタスクを処理するようにチップの構造を強調しています。中央には、メイン接続ハブとして機能するグローバルルーティングプール(GRP)があり、さまざまなロジックと機能ブロックをリンクするため、信号がデバイス全体で効率的に移動できます。GRPの両側には、sysclockシステムの一部である2つの位相ロックループ(PLL0およびPLL1)があります。これらは、チップ全体の高速操作のタイミング精度を維持するのに役立つ正確で調整可能なクロック信号を生成します。

GRPおよびPLLの周りには、4つのSysio Banksがあります。各銀行には、構成可能なシステムアレイ(CSA)と多機能ブロック(MFB)が含まれています。CSAは基本的なロジック処理を処理しますが、MFBは数学操作やメモリ関数などのより高度な機能をサポートしています。この配置により、デバイスはI/Oの柔軟性が強くなり、さまざまなアプリケーションのスケーリングが容易になります。パワーとクロックの接続も図に明確に示されています。複数のVCC、VREF、およびGNDピンは、チップ全体に安定した電力を維持するために分布しています。グローバルクロック入力(GCLK0〜GCLK3)により、外部クロックがシステムにフィードし、GRPおよびPLLと連携することができます。

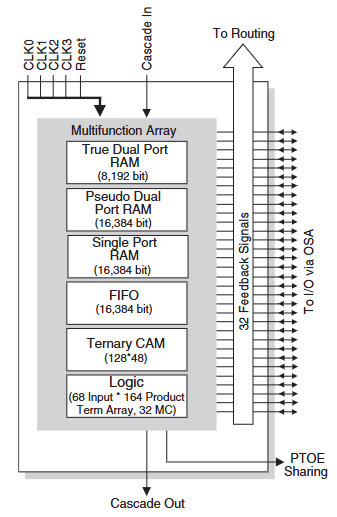

多機能ブロック(MFB)図

LC5768MC-75F256C ISPXPLD 5000MX/5000MCの多機能ブロック(MFB)は、メモリ関数とロジック関数の両方を組み合わせて、柔軟な設計ニーズをサポートします。真のデュアルポートRAM(8,192ビット)、擬似デュアルポートRAM、FIFO、およびシングルポートRAM(それぞれ16,384ビットまで)、および三元カム(128×48)を含むいくつかのメモリタイプをサポートします。これらのメモリオプションにより、MFBはデータバッファリング、一時的なストレージ、高速データ検索に役立ちます。

MFBには強力なロジック機能もあります。164個の製品用語アレイと32個のマクロセルによる68入力が含まれているため、複雑なロジック操作を実行できます。複数のクロック入力(CLK0からCLK3)とリセット信号を使用して、タイミングと操作を制御します。機能を拡張するために、カスケードイン/アウトポートにより、MFBをブロック全体に接続できます。QSA(Quad System Array)インターフェイスは、外部システムとの迅速な通信のためにMFBをI/Oバンクに接続します。要するに、MFBは、メモリタスクとロジックタスクの両方を処理する強力で柔軟なユニットであり、埋め込まれた高速アプリケーションでデバイスのパフォーマンスをうまく機能させます。

LC5768MC-75F256C仕様

|

タイプ |

パラメーター |

|

メーカー |

Lattice Semiconductor Corporation |

|

シリーズ |

ISPXPLD®5000 |

|

パッケージング |

バルク |

|

パーツステータス |

アクティブ |

|

プログラム可能なタイプ |

プログラム可能なシステムで |

|

遅延時間TPD(1)最大 |

7.5 ns |

|

電圧供給 - 内部 |

1.65V〜1.95V |

|

ロジック要素/ブロックの数 |

24 |

|

マクロセルの数 |

768 |

|

I/Oの数 |

193 |

|

動作温度 |

0°C〜90°C(TJ) |

|

取り付けタイプ |

表面マウント |

|

パッケージ /ケース |

256-BGA |

|

サプライヤーデバイスパッケージ |

256-FPBGA(17x17) |

LC5768MC-75F256Cアプリケーション

1.通信とネットワーキング

LC5768MC-75F256Cは、高速で決定論的ロジックが必要なベースステーション、通信スイッチ、および光ネットワークユニットでの使用に最適です。その組み込みメモリとマルチボルテージI/Oサポートは、プロトコル処理、データフレーミング、および低遅延制御タスクを有効にします。

2.データ通信とストレージ

このCPLDは、効率的なデータ処理と高速信号処理を必要とするルーター、RAIDコントローラー、およびディスクアレイシステムに適しています。デュアルポートSRAMおよびFIFOサポートは、ハイスループット環境で必要なバッファリングとフロー制御を提供します。

3.プロトコルプロセッサとバスインターフェイス

予測可能なタイミングと高密度ロジックリソースを備えたLC5768MCは、バスブリッジ、バックプレーンインターフェイス、およびプロトコルデコーダの実装に優れています。これにより、迅速なロジック応答が可能になり、複数のシグナリング基準とのシームレスな統合がサポートされます。

4.産業およびIoT制御システム

産業用自動化では、デバイスは監視、機械制御、ロジックシーケンスに使用されます。インスタントオン機能、低電力の抽選、および堅牢なI/O機能により、IoTノードと埋め込みコントローラーに適しています。

5.消費者および医療用電子機器

コンパクトなフットプリントとリッチロジックミックスメモリ機能により、このCPLDはポータブル医療機器と家電製品で価値があります。サイズが制約されたエネルギーに敏感な設計におけるシステム制御、インターフェイス管理、および電源シーケンスを処理します。

LC5768MC-75F256C同様の部品

|

特徴 |

LC5768MC-75F256C |

LC5768MV-75F484C |

LC5768MV-75FN256C |

LC5768MV-5F484C |

|

家族 |

ISPXPLD 5000MC |

ISPXPLD 5000MV |

ISPXPLD 5000MV |

ISPXPLD 5000MV |

|

コア電圧 |

1.8V |

3.3V |

3.3V |

3.3V |

|

マクロセル |

768 |

768 |

768 |

768 |

|

最大周波数 |

〜150MHz |

〜150MHz |

〜150MHz |

〜200〜250MHz |

|

伝播遅延(TPD) |

7.5ns |

7.5ns |

7.5ns |

5ns |

|

パッケージタイプ |

256ボールBGA |

484ボールBGA |

256ボールBGA |

484ボールBGA |

|

パッケージコード |

F256C |

F484C |

FN256C |

F484C |

|

I/Oカウント |

193 |

317 |

193 |

317 |

|

インシステムプログラム可能 |

はい |

はい |

はい |

はい |

|

埋め込まれたメモリサポート |

はい(sram/fifo/cam) |

はい |

はい |

はい |

|

JTAG(IEEE 1149.1) |

サポート |

サポート |

サポート |

サポート |

|

インスタントオン |

はい |

はい |

はい |

はい |

|

応用 |

低電力、密な論理 |

高いI/O、一般的なCPLD |

コンパクト3.3Vロジック |

高速3.3Vロジック |

LC5768MC-75F256Cプログラミング手順

1.ボードとツールを準備します

格子HW-USBN-2Bなどの互換性のあるプログラミングケーブルを使用して、LC5768MC-75F256CをPCに接続します。JTAGラインが適切にルーティングされ、終了抵抗器(たとえば、TCKの4.7kΩ)が設置されていることを確認して、安定した通信を確保します。

2.プログラミングファイルを生成します

格子ダイヤモンドまたはISPVMソフトウェアを使用して、設計をコンパイルし、JEDEC(.JED)プログラミングファイルをエクスポートします。このファイルには、CPLDの構成メモリに書き込まれる完全なビットストリームが含まれています。

3.プログラミングソフトウェアを起動します

PCでダイヤモンドプログラマーまたはISPVMシステムツールを開き、プログラマーが適切に検出されていることを確認します。リストからLC5768MC-75F256Cデバイスを選択して、セットアップを開始します。

4.システム内プログラミング(ISP)を実行する

JTAG(IEEE 1532)インターフェイスを使用して、ボードにマウントされたままのJEDECファイルをデバイスに直接ロードします。BitStreamは内部の不揮発性メモリに保存され、起動時にインスタントオン構成を可能にします。

5.構成を確認して保護します

プログラミング後、構成が成功したことを確認するために読み取りバック操作を実行します。必要に応じて、セキュリティヒューズをアクティブにしてデバイスをロックし、不正な再プログラミングまたはリバースエンジニアリングを防ぎます。

6.デバイスを構成してリセットします

プログラミングが完了したら、デバイスが自動的に再起動するか、プログラムまたはINITピンを切り替えてリロードを強制することができます。その後、CPLDは、決定論的なスタートアップタイミングを備えた新しく適用された構成に基づいて動作します。

7.オプション:フィールドの再プログラミングまたは更新

更新または修正のために同じJTAGインターフェイスを使用して、フィールドでLC5768MC-75F256Cを再プログラムできます。さらに、SYSCONFIG™インターフェイスにより、高度なアプリケーションでのフルパワーサイクリングなしで部分的な再構成が可能になります。

LC5768MC-75F256C利点

• ポータブルおよび組み込みシステムの電力操作の低下

コア電圧が高い多くの従来のCPLDと比較して、LC5768MC-75F256Cの低電力1.8Vコアは、システム全体の消費電力を削減するのに役立ちます。これにより、熱予算とエネルギー効率が重要なバッテリー操作または熱に敏感なアプリケーションにとって魅力的です。

• インスタントオン機能

すべてのスタートアップで外部構成を必要とする多くのFPGAまたはより大きなプログラム可能なデバイスとは異なり、このCPLDはインスタントオンの動作を提供し、遅延や外部フラッシュメモリの必要性を回避できます。これにより、操作までの時間と信頼性の向上につながります。

• より予測可能なタイミング対FPGA

このCPLDの決定論的タイミング挙動は、特に重い論理またはI/O荷重の下で、より大きなFPGAの頻繁に変数のタイミングと比較してより良い制御を与えます。これにより、デジタル制御ループ、通信インターフェイス、同期ロジックシステムなどの時間的に重要なアプリケーションに適しています。

• 効率的な学習曲線および設計ツールエコシステム

22V10、古いPAL/GAL、または単純なPLDからの移行のために、このデバイスは、DiamondやISPVMなどの格子の直感的な設計ツールを介して穏やかな学習曲線を提供します。多くの人は、より高速なプロトタイピングと統合の頭痛の減少から利益を得ています。

LC5768MC-75F256Cパッケージングの寸法

• パッケージタイプ:ファインピッチボールグリッドアレイ

• ピンカウント:256ボール

• パッケージサイズ:17mm×17mm

• パッケージの高さ:約1.2mm

• ボールピッチ:標準のファインピッチは通常0.8mmです

LC5768MC-75F256Cメーカー

LC5768MC-75F256Cは製造されています Lattice Semiconductor Corporation、米国に拠点を置く会社は、低電力の小型プログラム可能なロジックデバイスの専門知識を認めました。1983年に設立され、オレゴン州ヒルズボロに本社を置くLatticeは、通信、コンピューティング、産業、自動車、および消費者市場のアプリケーションに合わせたFPGA、CPLD、および関連する開発ツールの提供に焦点を当てています。同社は、長い製品のライフサイクル、幅広い設計ツールのサポート、およびデバイスファミリ全体で信頼できるシステム内プログラマ性で知られています。ISPXPLD®5000MCファミリーの元の開発者およびサプライヤーとして、Latticeは、認定されたディストリビューターおよび長期ライフサイクルパートナーを通じて、堅牢な技術文書、ソフトウェアサポート、および可用性を保証します。

結論

LC5768MC-75F256Cは、1つのコンパクトチップで強力なロジックとメモリ機能を提供するスマートで信頼性の高いCPLDです。パワーをほとんど使用し、即座に起動し、さまざまな信号タイプで動作します。768個のマクロセル、組み込みのメモリ、高速クロック、柔軟な入出力オプションにより、通信デバイス、産業機械、貯蔵システム、家電などの製品に適しています。簡単なプログラミング、強力なパフォーマンス、および更新のサポートにより、新しいデザインとアップグレードの両方に役立つソリューションになります。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1.バッテリー駆動またはエネルギーに敏感なデバイスでLC5768MC-75F256Cを使用できますか?

はい、LC5768MC-75F256Cの1.8Vコア電圧と低電力設計により、IoTノードや医療デバイスなどのポータブル、バッテリー操作、および熱的に制約された環境に非常に適しています。

2。LC5768MC-75F256Cはレガシー5Vシステムと互換性がありますか?

はい。コア電圧が低い場合でも、LC5768MC-75F256Cは5V耐性のI/Oバンクを備えており、追加のレベルシフトコンポーネントを必要とせずにレガシーインターフェイスと混合電圧システムとの互換性を確保します。

3. LC5768MC-75F256Cプログラミングにはどのような開発ツールがサポートされていますか?

LC5768MC-75F256Cは、Lattice Diamond、ISPVMシステム、およびダイヤモンドプログラマーによってサポートされています。これらのツールは、エントリーレベルと高度なユーザーの両方に適した設計、シミュレーション、プログラミング、デバッグを完全にサポートします。

4. LC5768MC-75F256Cは、外部メモリを動作させる必要がありますか?

構成には外部メモリは必要ありません。LC5768MC-75F256Cには不揮発性メモリがあり、インスタントオン機能をサポートしているため、外部フラッシュやEEPROMを必要とせずにパワーアップの直後に動作を開始できます。

5。LC5768MC-75F256Cは、過酷な産業環境に適していますか?

はい、堅牢なロジックパフォーマンス、広い電圧耐性、信頼性の高いスタートアップ動作により、LC5768MC-75F256Cは、産業制御システムと安定した操作が必要な工場自動化でうまく機能します。

EPF8820ARC208-4 FPGAガイド:機能、アーキテクチャ、アプリケーション、およびプログラミング

07/11/2025で公開されています

EPF6016ATC144-2N FPGA:機能、プログラミング、アプリケーション、および代替案

07/10/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/18/8000で公開されています 147770

-

USB-Cピンアウトと機能

04/18/2000で公開されています 112006

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/18/1600で公開されています 111351

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/18/0400で公開されています 83768

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79564

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66959

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63098

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63040

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54096

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52184