ラッチとフリップフロップ: デジタル エレクトロニクスの比較ガイド

ラッチとフリップフロップは、回路内でバイナリ データを保存および制御するのに役立つ基本的なデジタル ストレージ要素です。この記事では、それらが何であるか、どのように機能するか、タイミング動作がどのように異なるかを学びます。また、それらの利点、制限、および一般的な用途についても説明します。これは、デザイン内でそれぞれをいつ使用するかを理解するのに役立ちます。カタログ

デジタルエレクトロニクスにおけるラッチとは何ですか?

図 1. 基本的なラッチ回路図

ラッチは、1 ビットのバイナリ データを格納するために使用されるレベル トリガーのデジタル ストレージ要素です。データをいつ保存または保持できるかを決定するイネーブル信号または制御信号に応答します。このため、基本的なデジタル電子機器の重要なコンポーネントとなっています。ラッチは通常、単純な論理ゲート構成を使用して実装されます。一時的なデータ保持が必要な回路で広く使用されています。

ラッチは、安定した出力値を維持できる基本的な記憶ユニットとして機能します。その構造により、制御条件によって更新が許可されるまで論理状態を保持できます。このため、デジタル システムでの単純なストレージおよび制御タスクに適しています。ラッチは、大規模なロジック設計の構成要素としてよく使用されます。そのシンプルさにより、複雑さの低い回路では効率的になります。

デジタルエレクトロニクスにおけるフリップフロップとは何ですか?

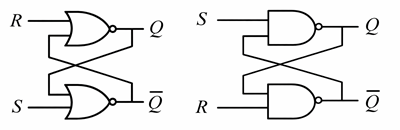

図 2. 基本的なフリップフロップ回路図

フリップフロップは、クロック信号に応答して 1 ビットのデータを記憶する、エッジ トリガーのデジタル記憶素子です。特定の信号遷移時にのみ状態を更新するように設計されています。この制御された動作により、現代のデジタル システムでは重要になります。フリップフロップは順序論理回路で広く使用されています。これらは、多くの電子設計においてコアコンポーネントとして機能します。

フリップフロップは、クロック イベント間で安定した出力を維持する信頼性の高いメモリ ユニットとして機能します。その設計により、データは制御された予測可能な方法で保存されます。さまざまなタイプのフリップフロップが、デジタル回路のさまざまな論理機能をサポートしています。これらのデバイスは一般に、複雑なシステムの構成要素として使用されます。構造化された動作により、組織化されたデータの処理に適しています。

ラッチとフリップフロップの動作 (タイミングとトリガ)

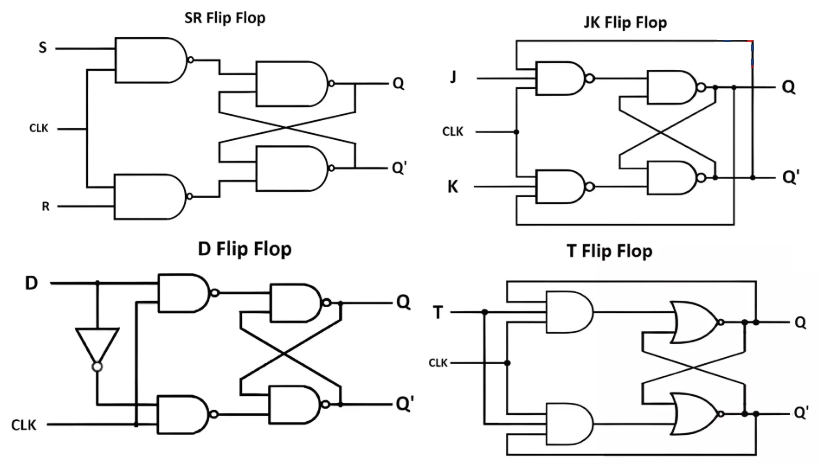

ラッチ状態の変化(レベルトリガー動作)

図 3. ラッチ レベルでトリガーされるタイミング図

波形内の強調表示されたアクティブ領域で示されているように、イネーブル信号がアクティブ レベルにある間、ラッチは状態を継続的に変更します。これらの間隔中、出力は入力に直接続き、更新が可能になります。この動作は、正レベルと負レベルの両方のトリガで明らかであり、ラッチは制御信号がハイかローかに基づいて応答します。イネーブル信号が非アクティブになると、出力は更新を停止し、最後に保存された値を保持します。この波形は、単一のアクティブ期間内に複数の入力変化が発生する可能性があり、すべてが出力に反映されることを示しています。この継続的な応答性は、レベル トリガー操作における透明性として知られています。その結果、ラッチの動作は単一の遷移点ではなく信号の継続時間に依存します。

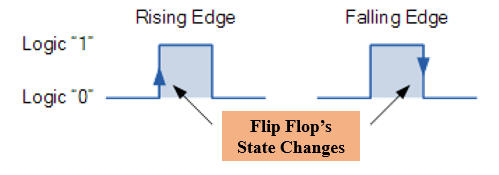

フリップフロップの状態変化 (エッジトリガー動作)

図 4. フリップフロップのエッジトリガーのタイミング図

フリップフロップは、波形の立ち上がりエッジと立ち下がりエッジで示されるように、クロック信号の特定の遷移点でのみ状態を変更します。出力はこれらのエッジで正確に更新され、その瞬間の入力値をキャプチャします。クロック遷移間では、入力の変動に関係なく、出力は変化しません。この動作により、明確に定義された瞬間にのみデータ変更が発生することが保証されます。この図は、遷移エッジが状態更新のトリガー ポイントとしてどのように機能するかを示しています。各エッジは、フリップフロップが新しいデータを格納する 1 つの機会を表します。このエッジ トリガー メカニズムにより、デジタル回路で制御された予測可能なタイミングが提供されます。

ラッチとフリップフロップの長所と短所

ラッチとフリップフロップの利点

• ラッチは、継続的な入力追跡により、より高速な応答を実現します。

• シンプルな設計では、ラッチの消費電力が低くなります。

• フリップフロップは、クロック同期による正確なタイミング制御を提供します。

• フリップフロップは、意図しない状態変化のリスクを軽減します。

• どちらも信頼性の高いシングルビット データ ストレージをサポートします。

• どちらも複雑なデジタル システムを構築するために重要です。

ラッチとフリップフロップの制限

• ラッチは、アクティブ イネーブル期間中にノイズの影響を受けやすくなります。

• ラッチは、複雑なシステムにおいてタイミングの不確実性を引き起こす可能性があります。

• フリップフロップにはより多くの回路が必要となり、複雑さが増します。

• フリップフロップはクロックを使用するため、より多くの電力を消費します。

• どちらもエラーを避けるために慎重なタイミング設計を必要とします。

• どちらも回路に伝播遅延を引き起こす可能性があります。

ラッチとフリップフロップの応用

1. データストレージレジスタ

レジスタはフリップフロップを使用して、プロセッサやデジタル システムに複数ビットのデータを保存します。これらは、計算およびデータ転送操作中に一時的に値を保持します。これにより、処理ステージ間の安定したデータ処理が保証されます。レジスタは、CPU 操作、バッファリング、データ同期に適しています。

2. カウンタとタイマー

フリップフロップは、イベントやクロック パルスを追跡するデジタル カウンターを構築するために広く使用されています。これらのカウンタは、タイミング回路、分周、デジタル クロックに優れています。これらにより、組み込みシステムでの正確な計数操作が可能になります。タイマーは遅延と定期的なアクションを制御するためにそれらに依存します。

3. デジタル回路の記憶素子

ラッチとフリップフロップは両方とも、デジタル電子機器の基本的なメモリ ユニットとして機能します。これらには、必要に応じてアクセスまたは変更できるバイナリ データが保存されます。この機能はシステム状態の保持に必要です。メモリ回路は安定した動作のためにこれらの要素に依存しています。

4. データ同期システム

フリップフロップは、複雑なシステム内の異なるクロック ドメイン間で信号を同期するのに役立ちます。これらにより、タイミング エラーやグリッチなしにデータが転送されることが保証されます。これにより、高速設計におけるシステムの信頼性が向上します。同期は通信ユニットと処理ユニットにおいて重要です。

5. 制御ロジック回路

ラッチは、入力変化に対する即時応答が必要な制御回路で使用されます。これらは、イネーブル信号、ゲート、ロジック フローの管理に役立ちます。これにより、デジタル設計での柔軟な制御が可能になります。制御ロジックにより、システムの適切な動作とシーケンスが保証されます。

6. シフトレジスタ

フリップフロップは、データを順番に移動するシフト レジスタを構築するために使用されます。これらは、データのシリアル化、通信システム、信号処理で使用されます。シフト レジスタにより、コンポーネント間の効率的なデータ転送が可能になります。デジタル通信インターフェースで広く使用されています。

フリップフロップとラッチの違い

|

アスペクト |

ラッチ |

フリップフロップ |

|

トリガー

仕組み |

いつ応答するか

イネーブル = HIGH または LOW (レベル依存) |

でのみ応答します

クロックエッジ(↑または↓) |

|

制御信号

タイプ |

有効にする(EN)

信号 |

クロック(CLK)

信号 |

|

データ更新

状態 |

アップデート

アクティブレベルの持続時間全体にわたって |

更新は 1 回につき 1 回

クロックエッジ |

|

入力サンプリング

窓 |

開いた窓

(期間ベース) |

インスタントサンプリング

(エッジベース、~ns 範囲) |

|

典型的な

伝播遅延 |

~1 ~ 5 ns (単純な

ゲート遅延) |

~5~20ns

(クロック回路を含む) |

|

回路

複雑さ |

4 ~ 6 個の論理ゲート

(基本的な SR ラッチ) |

10 ~ 20 以上のゲート

(エッジトリガーデザイン) |

|

パワー

消費 |

下位 (いいえ

連続クロック切り替え) |

より高い(理由により)

クロックの遷移) |

|

スイッチング

周波数制限 |

入力による制限

イネーブル時の安定性 |

操作できる

100 MHz ~ GHz の範囲で確実に動作 |

|

グリッチ

感度 |

期間中は高くなります

アクティブイネーブル期間 |

~による低下

エッジアイソレーション |

|

タイミング制御

精度 |

依存している

信号持続時間を有効にする |

定義者

正確なクロックエッジ |

|

データの安定性

(ホールド動作) |

以降保持

イネーブルが非アクティブになります |

次まで保留

クロックエッジ |

|

時計

要件 |

不要 |

必須

操作 |

|

デザインスタイルフィット |

非同期または

シンプルな制御ロジック |

同期

デジタルシステム |

|

スケーラビリティ

システム |

スケーラビリティが低い

大きなデザインの場合 |

拡張性が高い

複雑なシステムで |

|

典型的な

実装用途 |

ゲート、シンプル

ストレージ、制御パス |

レジスター、

カウンター、パイプライン |

結論

ラッチとフリップフロップはどちらも重要な 1 ビット記憶素子として機能しますが、主に入力信号とタイミング制御への応答方法が異なります。ラッチはレベルトリガー動作を通じて高速で継続的な応答を提供し、フリップフロップはエッジトリガー動作を通じて正確で安定したデータ処理を提供します。それぞれに、電力、複雑さ、信頼性の点で独自の利点とトレードオフがあります。どちらを選択するかは、タイミング要件、システム タイプ、およびデジタル エレクトロニクスにおける全体的な設計目標によって異なります。

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1. 同期ストレージ要素と非同期ストレージ要素の主な違いは何ですか?

フリップフロップのような同期要素はクロック信号に依存しますが、ラッチのような非同期要素はクロックなしで入力レベルに基づいて動作します。

2. クロックデジタルシステムではなぜフリップフロップが好まれるのですか?

フリップフロップは、定義されたクロックエッジでのみデータが変更されることを保証し、システムのタイミングを予測可能にし、エラーを削減します。

3. ラッチをフリップフロップに変換できますか?

はい、マスター/スレーブ構成で 2 つのラッチを組み合わせると、エッジ トリガー動作のフリップフロップを作成できます。

4. デジタル回路で使用される一般的なタイプのフリップフロップは何ですか?

一般的なタイプには SR、JK、D、および T フリップフロップがあり、それぞれが特定のロジックおよび制御機能用に設計されています。

5. タイミングの問題はラッチベースの設計にどのような影響を与えますか?

ラッチではイネーブル期間中に複数の入力変更が許可されるため、タイミングが不適切だとグリッチや競合状態が発生する可能性があります。

サイクロコンバーターの説明: 動作と使用方法の簡単なガイド

04/3/2026で公開されています

電子システム設計のための LGA と BGA の比較ガイド

04/1/2026で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/18/8000で公開されています 147780

-

USB-Cピンアウトと機能

04/18/2000で公開されています 112042

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/18/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/18/0400で公開されています 83806

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79605

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66983

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63113

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63048

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54097

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52199