TMS320C6421ZWT5 DSPの概要:機能、代替、仕様、およびアプリケーション

この記事では、テキサスインスツルメンツが作成したデジタル信号プロセッサ(DSP)であるTMS320C6421ZWT5について学びます。それが何であるか、それがどのように機能するか、そして異なるシステムで役立つ重要な機能を説明します。また、図、仕様、アプリケーション、およびプログラミングのための簡単な手順も表示されます。最後に、このチップがどこで、なぜ使用されるのかを理解するでしょう。カタログ

TMS320C6421ZWT5とは何ですか?

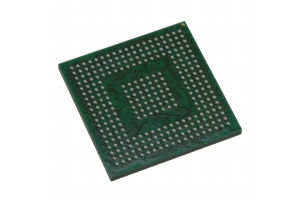

TMS320C6421ZWT5 TMS320C64X+ファミリの一部としてテキサスインストゥルメントによって開発された高性能デジタル信号プロセッサ(DSP)です。Velociti.2 Vliwアーキテクチャの上に構築されたこのデバイスは、最新の組み込みシステムでの集中的な信号処理のために設計された強力な固定点処理パフォーマンスを提供します。クロック速度が最大500 MHzに達すると、サイクルごとに複数の命令を実行できるため、幅広い高度な処理タスクに適しています。より広いTMS320C6000 DSPプラットフォームに属するC6421シリーズは、テキサスインスツルメンツのスケーラブルでコード互換のソリューションに焦点を当てています。世界中で信頼できるプロセッサの実績のあるファミリーの一環として、TMS320C6421ZWT5は長期設計の信頼できる基盤を提供します。

TMS320C6421ZWT5をお探しですか?現在の在庫、リードタイム、価格を確認するには、お問い合わせください。

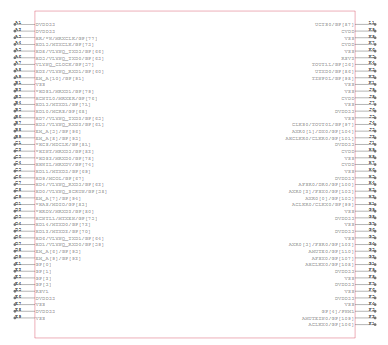

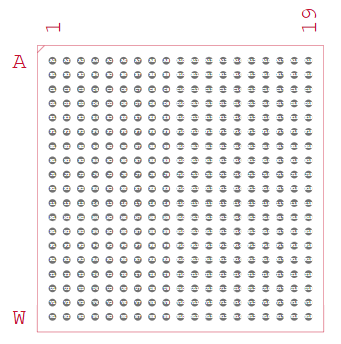

TMS320C6421ZWT5 CADモデル

TMS320C6421ZWT5シンボル

TMS320C6421ZWT5フットプリント

TMS320C6421ZWT5 3Dモデル

TMS320C6421ZWT5機能

• 高性能DSPコア

このデバイスは、velociti.2™vliwコアを搭載しており、1つのサイクルで最大8つの命令を実行できます。このアーキテクチャにより、非常に高いスループットが可能になり、複雑な信号処理タスクに最適です。

• 効率的な乗数とアルス

6つの算術ロジック単位(ALU)と2つの強力な乗数を統合し、複数の操作を同時に処理できます。この設計は、フィルタリング、変調、エンコーディングなどの集中的な数学操作をサポートします。

• 柔軟なオンチップメモリ

プロセッサには、16 KBのプログラムキャッシュ、48 kbのデータキャッシュ、64 kbの統一されたL2メモリが含まれます。これらの内部リソースは、遅延を減らし、アプリケーションのより速い実行をサポートします。

• DDR2およびフラッシュメモリインターフェイス

チップは、16ビットDDR2 SDRAMコントローラーと、NORやNANDフラッシュなどの外部メモリ用の8ビットの非同期EMIFを備えています。この柔軟性により、より大きなアプリケーションのメモリを拡張できます。

• 汎用性の高い周辺サポート

UART、I²C、MCBSP、SPDIF付きMCASP、16ビットホストポートインターフェイスなど、幅広いインターフェイスを提供します。これらにより、プロセッサは通信、オーディオ、産業システムに非常に適応性があります。

• 強化されたDMAコントローラー(EDMA)

64チャンネル強化DMAコントローラーは、メモリと周辺機器の間の高速データ転送をサポートします。これにより、CPU負荷が削減され、システム全体のパフォーマンスが向上します。

• ネットワーキングと接続

このチップは、10/100イーサネットMACをMII/RMIIサポートと外部接続用のVLYNQインターフェースと統合します。これらの機能により、ネットワーク対応の埋め込みアプリケーションに適しています。

• 豊富な汎用I/o

最大111の多重化GPIOピンと3つのPWM出力を備えたDSPは、システム制御とカスタムインターフェースに優れた柔軟性を提供します。これにより、幅広いハードウェア設計への簡単な統合が保証されます。

• 低電圧動作

1.05 Vまたは1.2 VおよびI/Oレベル1.8 Vまたは3.3 Vのコア電圧で動作します。この電力効率と柔軟性のバランスにより、組み込みデザインで信頼性が高くなります。

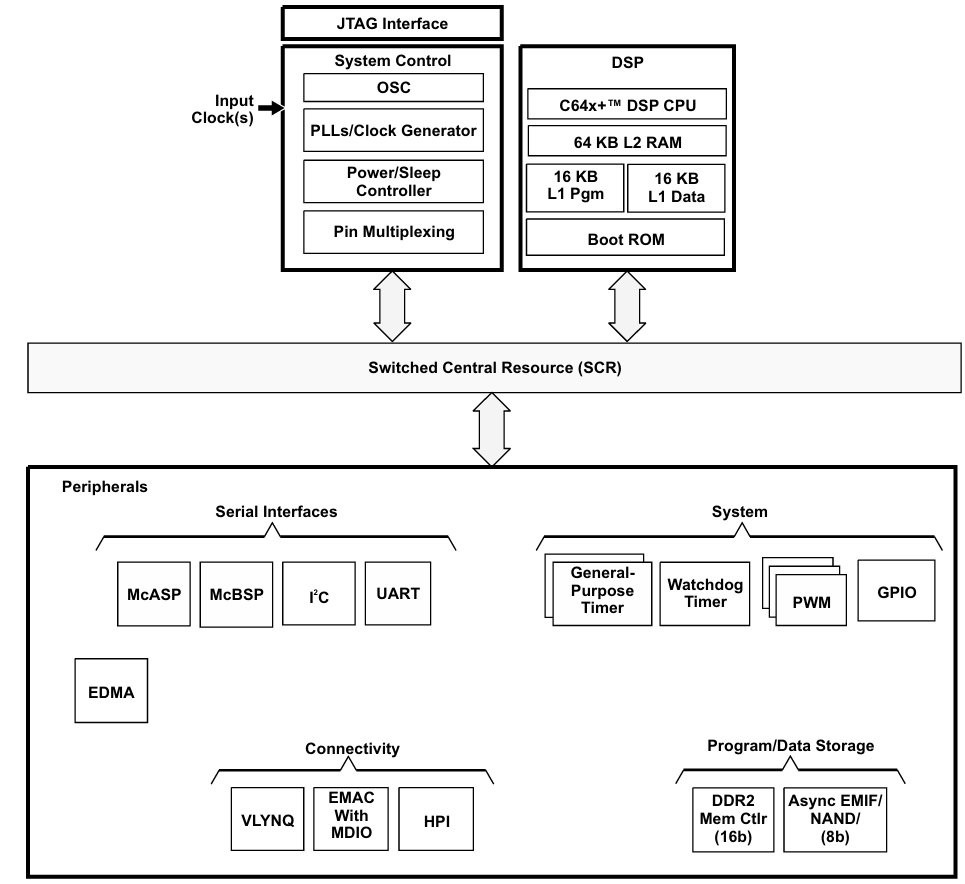

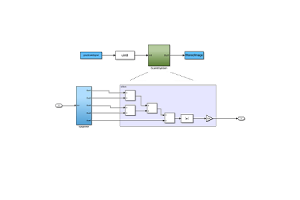

TMS320C6421機能ブロック図

TMS320C6421ZWT5機能ブロック図は、プロセッサがコア、メモリ、周辺機器を組み合わせて協力する方法を強調しています。中央には、L1およびL2メモリとブートROMを備えたC64X+ DSP CPUがあり、データアクセスとクイックスタートアップを保証します。発振器、PLL、電源管理などのシステム制御ブロックは、時計の生成、低電力モード、信号ルーティングを処理します。

すべての部品は、データフロー用のメインバスのように機能するスイッチセントラルリソース(SCR)を介してリンクされています。プロセッサには、高速データ転送のために強力なEDMAコントローラーによってサポートされるUART、I²C、MCBSP、MCASPなどのシリアルインターフェイスが含まれています。また、一般的なシステム制御用のタイマー、ウォッチドッグ関数、PWM、およびGPIOも備えています。

接続のために、このデバイスはMDIO、VLYNQ、およびホストポートインターフェイスを備えたイーサネットMACを提供し、ネットワーキングと外部通信に柔軟に対応できます。メモリの拡張は、DDR2メモリコントローラーとNANDまたはFlash用の非同期EMIFを介してサポートされます。一緒に、これらのブロックは、効率的なメモリと幅広い接続オプションで集中処理を処理するようにチップがどのように構築されているかを示しています。

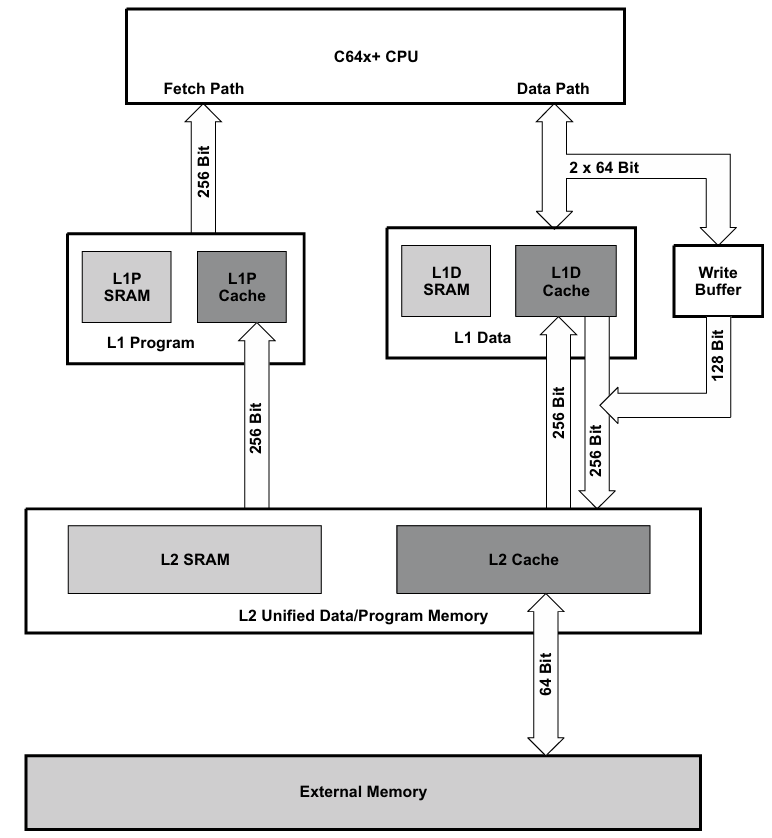

C64x+キャッシュメモリアーキテクチャ

TMS320C6421ZWT5のC64X+キャッシュメモリアーキテクチャは、CPUが命令とデータへの高速アクセスを提供するために構築されています。L1メモリから始まります。これは、命令のL1プログラム(L1P)とデータのL1データ(L1D)の2つの部分に分割されます。どちらもSRAMとキャッシュが含まれ、CPUに接続されており、高速転送用の広い256ビットパスがあります。

この背後には、L2メモリは、データとプログラムの両方のためのより大きく統一されたスペースとして機能します。SRAMとキャッシュがあり、64ビットバスを介して外部メモリに接続します。書き込みバッファーは、バックグラウンドで書き込みを処理することにより、データストレージを高速化するのに役立ちます。この層状設計は、必要に応じてより大きな外部メモリへのアクセスを可能にしながら、頻繁に使用されるデータをCPUに近づけます。

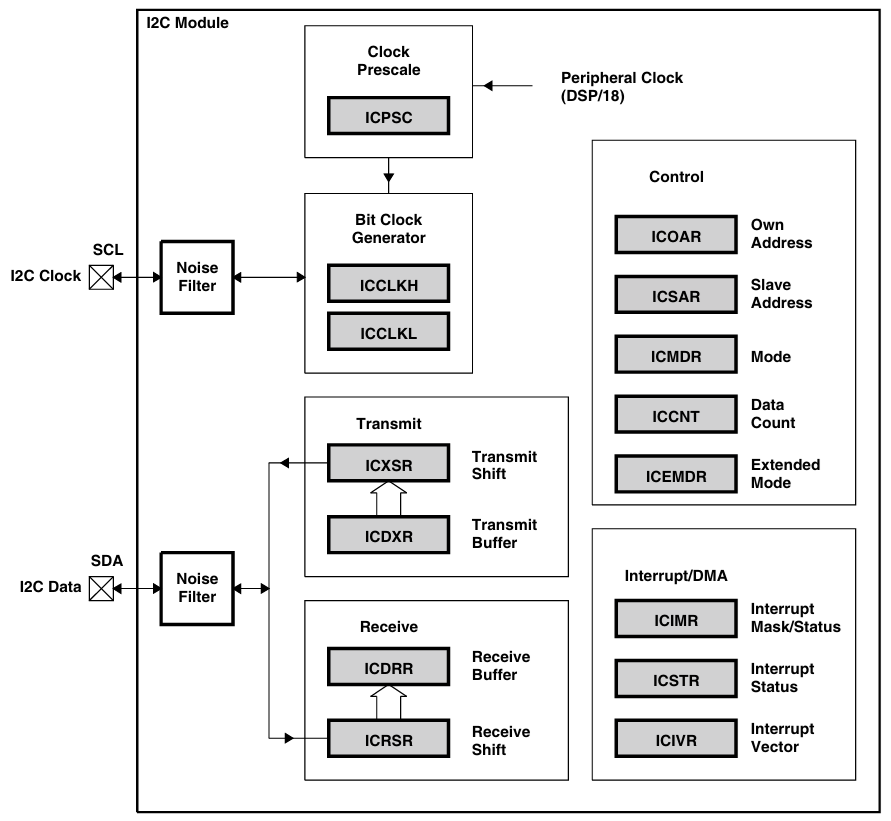

I2Cモジュールブロック図

TMS320C6421ZWT5のI²Cモジュールは、2つのI²Cラインを介した通信を制御します。両方の信号がノイズフィルターを通過して、転送を安定させます。クロックプリスケーラーとビットクロックジェネレーターは、通信のために正しい速度を設定します。

モジュールには、データを送信および受信するための個別のパスがあります。送信ブロックは、送信する前にバッファーにデータを保持しますが、CPUに渡す前に受信ブロックストアが着信します。コントロールユニットは、アドレス、モード、およびデータカウントを管理するため、デバイスはマスターまたはスレーブとして機能します。

また、割り込みサポートとDMAサポートも含まれています。これは、CPUが絶えずチェックする必要なく、データ転送を自動的に処理するのに役立ちます。これにより、I²CインターフェイスがDSPを外部デバイスに接続するために信頼性が高く効率的になります。

TMS320C6421ZWT5仕様

|

タイプ |

パラメーター |

|

メーカー |

テキサスの楽器 |

|

シリーズ |

TMS320C642X |

|

パッケージング |

トレイ |

|

パーツステータス |

アクティブ |

|

タイプ |

固定点 |

|

インタフェース |

HPI、I2C、MCASP、MCBSP、UART、10/100イーサネットMAC |

|

クロックレート |

500 MHz |

|

不揮発性メモリ |

ROM(64 kb) |

|

オンチップRAM |

96 kb |

|

電圧-I/O |

1.8 V、3.3 v |

|

電圧 - コア |

1.05 V、1.20 V |

|

動作温度 |

0°C〜90°C(TJ) |

|

取り付けタイプ |

表面マウント |

|

パッケージ /ケース |

361-LFBGA |

|

サプライヤーデバイスパッケージ |

361-NFBGA(16×16) |

|

基本製品番号 |

TMS320 |

TMS320C6421ZWT5アプリケーション

1。テレコムおよびワイヤレスシステム

TMS320C6421ZWT5は、高速信号処理能力のため、通信インフラストラクチャおよびワイヤレスデバイスで広く使用されています。変調、復調、チャネルコーディングなどのタスクを処理します。これらは、ベースステーション、ゲートウェイ、ブロードバンド機器で適しています。統合されたイーサネットMACおよびDDR2サポートにより、接続性と通信に必要なメモリ帯域幅の両方を提供します。

2。オーディオおよび信号処理

このDSPは、高性能計算と低遅量処理を必要とするオーディオシステムに適しています。マルチチャネル音声コーデックを実行し、ノイズキャンセルを実行し、時間内にオーディオ効果を処理できます。MCBSPやMCASPなどのインターフェイスにより、オーディオ機器に簡単に接続できるようになり、信頼性の高い高品質のサウンドパフォーマンスが確保されます。

3。イメージングおよびビデオアプリケーション

C6421は、迅速なデータ処理を必要とするイメージングおよびビデオタスクにも適用できます。そのDSPコアを使用すると、カメラ、監視システム、埋め込まれたビジョンデバイスの圧縮、減圧、および強化機能をサポートできます。並列実行機能を活用することにより、画像ストリームとビデオストリームを効率的に処理できます。

4。産業および組み込み制御

産業およびオフィスの自動化では、このデバイスは、タイマー、GPIO、PWM、およびDMAの統合について評価されています。プリンター、スキャナー、モーターコントローラー、埋め込み自動化ユニットなどのアプリケーションで使用されます。その効率的な電力モードと高速処理は、エネルギー消費を低く抑えながら、信頼できるパフォーマンスを提供するのに役立ちます。

TMS320C6421ZWT5同様の部品

|

仕様 |

TMS320C6421ZWT5 |

TMS320C6421ZDU5 |

TMS320C6421ZDU4 |

TMS320C6421ZWTQ5 |

TMS320C6424 |

|

コアアーキテクチャ |

c64x+ velociti.2 vliw dsp |

c64x+ velociti.2 vliw dsp |

c64x+ velociti.2 vliw dsp |

c64x+ velociti.2 vliw dsp |

c64x+ velociti.2 vliw dsp |

|

クロック速度 |

500 MHz |

500 MHz |

600 MHz |

500 MHz |

最大720 MHz(より高いティア) |

|

パフォーマンス(MIPS) |

500 MHzで〜4,000 |

500 MHzで〜4,000 |

600 MHzで〜4,800 |

500 MHzで〜4,000 |

より高い、最大8,000 MIP |

|

オンチップメモリ |

L1P 16 KB、L1D 48 KB、L2 64 KB |

L1P 16 KB、L1D 48 KB、L2 64 KB |

L1P 16 KB、L1D 48 KB、L2 64 KB |

L1P 16 KB、L1D 48 KB、L2 64 KB |

利用可能なより大きなL2オプション |

|

ROMサイズ |

64 KBブートROM |

64 KBブートROM |

64 KBブートROM |

64 KBブートROM |

64 KBブートROM |

|

外部メモリサポート |

DDR2(16ビット)、EMIFA(8ビット) |

DDR2(16ビット)、EMIFA(8ビット) |

DDR2(16ビット)、EMIFA(8ビット) |

DDR2(16ビット)、EMIFA(8ビット) |

DDR2(16ビット)、EMIFA(8ビット) |

|

イーサネットMac |

MDIOを使用した10/100 MB/s |

MDIOを使用した10/100 MB/s |

MDIOを使用した10/100 MB/s |

MDIOを使用した10/100 MB/s |

MDIOを使用した10/100 MB/s |

|

動作温度 |

0°Cから90°C(商業) |

0°Cから90°C(商業) |

0°Cから90°C(商業) |

–40°Cから+125°C(産業) |

0°Cから90°C(商業) |

|

パッケージ |

361ピンNFBGA(16×16 mm) |

361ピンnfbga(diff。Marking) |

361ピンnfbga |

361ピンnfbga |

361ピンnfbga |

|

アプリケーション |

テレコム、オーディオ、埋め込み |

テレコム、オーディオ、埋め込み |

パフォーマンスクリティカルな通信 |

産業/過酷な環境 |

ハイエンドテレコム&voip |

TMS320C6421ZWT5プログラミング手順

通常、このプロセスは、環境のセットアップから、最適化されたDSPコードの書き込み、デバッグ、展開に移行します。

1.開発ツールをインストールします

最初のステップは、TIの統合開発環境であるCode Composer Studio(CCS)をセットアップすることです。このソフトウェアは、C6000 DSPファミリ向けに特別に設計されたコンパイラ、アセンブラ、デバッガー、およびプロジェクト管理ツールを提供します。このセットアップがなければ、DSPハードウェアのプログラミングとテストは不可能です。

2。新しいプロジェクトを作成します

CCSでは、TMS320C6421デバイス用に構成された新しいプロジェクトを作成することから始めます。これには、適切なコンパイラオプション、リンカーコマンドファイル、スタートアップコードテンプレートの選択が含まれます。正しいプロジェクトのセットアップにより、メモリマップとシステムリソースがハードウェアに合わせて保証されます。

3.アプリケーションコードを書きます

アプリケーションは、一般的なロジックの場合はCで、またはパフォーマンス批判的なルーチンのアセンブリに記述できます。多くの人がC64X+ VLIWアーキテクチャを利用しており、複数の命令が並行して実行できるようにします。ループを最適化し、DSP固有の内因性を使用すると、効率を大幅に改善できます。

4.コンパイルと最適化

コーディング後、プログラムはコンパイルされ、機械の命令に組み立てられます。TIのコンパイラには、ソフトウェアのパイプライン化やループの展開などの最適化機能が含まれており、スループットを最大化します。この段階では、プログラマーは、実行速度とメモリ使用量がアプリケーションの要件を満たすことを保証します。

5。リンクと負荷

コンパイルされたオブジェクトファイルは、デバイスのメモリマップに従ってリンクされ、正しい内部および外部メモリ領域にコードとデータを配置します。リンクしたら、バイナリはJTAGデバッガーを介してDSPにロードされます。これにより、システムがハードウェアで実行される準備ができます。

6.ハードウェアでデバッグ

CCSを使用して、Breakpointsを設定し、レジスタを監視し、DSPが実行されている間に命令を踏むことができます。ハードウェアでのデバッグにより、キャッシュの使用、割り込み、データ転送などの動作が明らかになります。このプロセスにより、実際の動作条件下でアプリケーションが正しく機能します。

7。展開と監視

テストが完了すると、プログラムはターゲットシステムでスタンドアロン実行のために展開されます。CCSを使用して、パフォーマンスを監視したり、メモリの割り当てを微調整したり、消費電力を削減したりできます。この最後のステップでは、DSPが確実に実行されており、実用的なアプリケーションの準備ができていることが確認されています。

TMS320C6421ZWT5の利点と短所

利点

•VLIW並列性を備えた高い固定点DSPパフォーマンス

•古いC6000デバイスとの上向きのコード互換性

•統合された周辺機器のリッチセットは、外部コンポーネントを削減します

•CCSと最適化ツールを備えた強力な開発エコシステム

•より高速なデータ処理のための柔軟なキャッシュとメモリアーキテクチャ

短所

•電力節約のための動的電圧または周波数スケーリングはありません

•低電力DSPと比較して、より高い消費電力

•安全なブーツまたは保護のための組み込みのセキュリティ機能がありません

•ポータブルまたはバッテリー駆動のアプリケーションにはそれほど適していません

•モバイル使用のための適応性が制限されたパフォーマンスプロファイルを固定しました

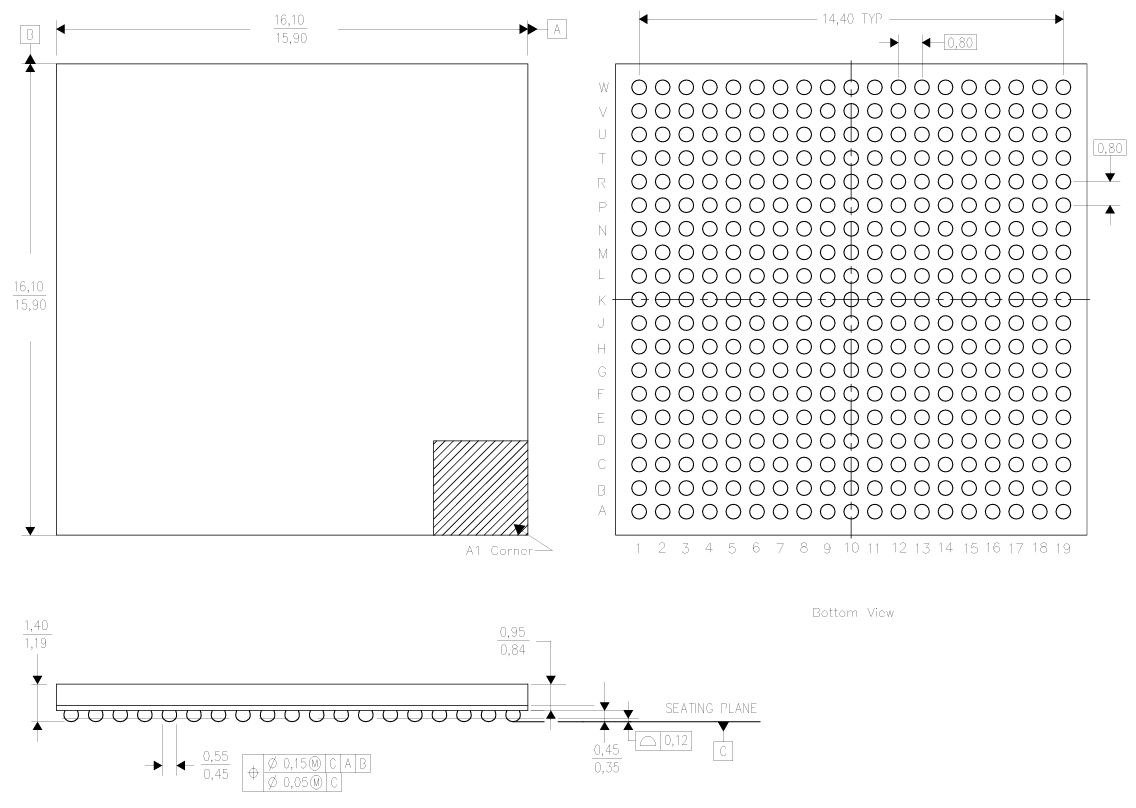

TMS320C6421ZWT5パッケージングの寸法

|

タイプ |

パラメーター |

|

パッケージタイプ |

NFBGA(361-Ball、ZWT) |

|

ボールグリッドアレイ |

16×16 |

|

ピンカウント |

361 |

|

全長(L) |

17.5 mm |

|

全体幅(W) |

15.45 mm |

|

ボディサイズの範囲 |

15.90 mm - 16.10 mm |

|

ボールピッチ |

0.80 mm |

|

ボールの直径 |

0.45 mm - 0.55 mm |

|

パッケージの高さ(h) |

1.19 mm - 1.40 mm |

|

ボールの高さ(スタンドオフ) |

0.35 mm - 0.45 mm |

|

座席機の耐性 |

±0.12 mm |

|

コーナーインデックス(A1) |

マークされた参照コーナー |

TMS320C6421ZWT5メーカー

TMS320C6421ZWT5は製造されています テキサス楽器(TI)、テキサス州ダラスに本社を置く大手アメリカの半導体会社。TIは、アナログおよび組み込み処理技術の革新で世界的に知られており、電気通信、自動車、産業自動化、家電などの幅広い業界を駆動するソリューションを提供しています。高性能デジタル信号プロセッサの開発に関する数十年の専門知識により、TIはTMS320ファミリーを信号処理アプリケーションの基礎として確立しています。同社はまた、包括的な設計ツール、ソフトウェア環境、およびドキュメントでサポートし、DSP製品を高度な組み込みシステムに信頼できる統合を確保しています。

結論

TMS320C6421ZWT5は、強力な固定点性能、柔軟なメモリシステム、および通信、オーディオ、ビデオ、自動化に厳しいアプリケーションに合うリッチな接続で際立っています。その設計により、コードコンポーザースタジオを通じて開発効率が高くなり、ハードウェアで最適化とデバッグするためのツールがあります。プロセッサは、優れたスケーラビリティ、強力な統合、幅広いサポートを提供しますが、一部の発電機能とセキュリティ機能をトレードオフします。全体として、TIのエコシステムと実績のあるC6000プラットフォームでサポートされているパフォーマンス、メモリ、およびインターフェイスの信頼できるバランスを提供し、高度な組み込みプロジェクトに実用的な選択肢となっています。

データシートPDF

TMS320C6421ZWT5データシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1。TMS320C6421ZWT5は古いTI DSPと互換性がありますか?

はい。以前のC6000デバイスとの上向きのコード互換性を維持しているため、既存のプロジェクトの再利用と開発サイクルの短縮に役立ちます。

2。TMS320C6421ZWT5は、低電力DSPとどのように比較されますか?

超低電力DSPよりも多くのパワーを消費しますが、はるかに高い処理スループット、より豊富な周辺機器、より高速なメモリインターフェイスを提供し、パフォーマンス集約型のデザインにより適しています。

3。TMS320C6421ZWT5は、ネットワークアプリケーションで使用できますか?

はい。統合された10/100イーサネットMACおよびVLYNQインターフェイスにより、プロセッサはネットワーク接続をサポートし、通信およびデータ共有環境でうまく機能することができます。

4。このDSPは外部メモリの拡張をサポートしていますか?

はい。TMS320C6421ZWT5には、DDR2 SDRAMコントローラーとEMIFインターフェイスが含まれており、より大きなストレージ要件のためにNORまたはNAND Flashへの接続を可能にします。

5。TMS320C6421ZWT5はマルチタスクをどのように処理しますか?

そのVLIWコアは、サイクルごとに最大8つの命令を実行し、EDMAがサポートして高速データ転送をサポートし、複数のタスクを同時に処理するのに効率的になります。

EPM1270F256C4N MAX II CPLD概要:機能、仕様、アプリケーション

08/28/2025で公開されています

MC9328MX21CVMプロセッサ:機能、仕様、アプリケーション、および代替案

08/26/2025で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/19/8000で公開されています 147783

-

USB-Cピンアウトと機能

04/19/2000で公開されています 112072

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/19/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/19/0400で公開されています 83831

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79644

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 67010

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63135

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63067

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54098

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52227