MPC8548EVUAUJ のブロック図とパフォーマンス機能について

MPC8548EVUAUJ は、ネットワーク システムにおける高速かつ安定したデータ移動を処理するように構築されています。これは、ルーター、スイッチ、ゲートウェイ、および 24 時間信頼性の高いパフォーマンスを必要とするその他の通信機器の内部にあります。32 ビット PowerPC e500 コアで動作し、最大 1.333 GHz の速度に達することができ、パケット処理とシステム制御のための確かな処理能力を提供します。ギガビット イーサネット ポート、メモリ制御、セキュリティ機能を内蔵しており、多くの重要な機能を 1 つのチップ上に保持しています。つまり、外部部品が減り、基板レイアウトがすっきりします。また、ハードウェア暗号化のサポートも利用できるため、速度を低下させることなく安全なデータ トラフィックを管理できます。このガイドでは、その機能、技術的な詳細、アプリケーション、および全体的な利点を明確かつシンプルな方法で説明します。カタログ

MPC8548EVUAUJの概要

の MPC8548EVUAUJ は、PowerPC e500 コア上に構築され、ネットワークおよび通信システム用に設計された 32 ビット組み込みマイクロプロセッサです。高いクロック速度をサポートし、メモリ制御、ギガビット イーサネット インターフェイス、PCI 接続、およびシリアル通信ポートを単一チップに統合します。このデバイスは、ルーター、スイッチ、無線基地局、産業用ゲートウェイのデータ ルーティング、パケット処理、システム制御を管理します。オンチップのセキュリティ アクセラレーションは暗号化されたデータ転送をサポートし、キャッシュ メモリは処理効率を向上させます。コンパクトなパッケージは、高密度の基板レイアウトや長期間の動作に適しています。MPC8548EVUAUJを探しています。現在の在庫、納期、価格を確認するにはお問い合わせください。

MPC8548EVUAUJの特徴

シングルコア 32 ビット PowerPC e500 アーキテクチャ

MPC8548EVUAUJ は、組み込みネットワーキングおよび通信プラットフォーム用に設計された 32 ビット PowerPC e500 コアを使用します。制御ロジック、データ ルーティング、およびプロトコル処理を単一の処理ユニット内で実行します。このアーキテクチャは、効率的な命令フローと予測可能なシステム動作をサポートし、継続的に動作するデバイスで安定したパフォーマンスを維持するのに役立ちます。その構造により、プロセッサは追加の処理コアを必要とせずにオペレーティング システムとネットワーク スタックを管理できます。

動作速度最大1.333 GHz

このプロセッサは最大 1.333 GHz の周波数で動作します。より高いクロック速度により、より高速なデータ処理がサポートされ、パケットベースのシステムでの処理遅延が軽減されます。安定したスループットが必要なルーター、ゲートウェイ、スイッチング機器でのトラフィック管理をよりスムーズに行うことができます。動作範囲が定義されているため、設計者はシステムのニーズに基づいてパフォーマンスと消費電力のバランスを取ることができます。

統合信号処理エンジン

統合された信号処理エンジンは、通信およびデータ処理タスクで使用される算術演算をサポートします。フィルタリング、エンコード、リアルタイム データ処理を伴うアプリケーションのパフォーマンスが向上します。この機能をチップ上に統合することで、このデバイスは外部信号処理コンポーネントの必要性を減らし、コンパクトなシステム設計の維持に役立ちます。

統合セキュリティエンジン

内蔵のセキュリティ エンジンは、暗号化および復号化機能のハードウェア サポートを提供します。また、安全なキーの作成と保護された通信セッションに使用される乱数ジェネレーターも含まれています。この機能により、ネットワーク機器は暗号化されたトラフィックをプロセッサ内で直接処理できるようになり、一貫したシステム動作を維持しながらデータ保護が向上します。

クアッド 10 100 1000 Mbps イーサネット インターフェイス

このデバイスには、10 Mbps、100 Mbps、および 1000 Mbps のデータ レートをサポートする 4 つのイーサネット コントローラが統合されています。これらのインターフェイスにより、外部コントローラーを使用せずに複数のネットワーク ポートに直接接続できます。統合されたイーサネット サポートにより、ボード レイアウトが簡素化され、コンポーネント数が削減され、同時に単一プロセッサ プラットフォーム内でのマルチポート通信が可能になります。

DDR DDR2 および SDRAM 用メモリ コントローラー

オンチップ メモリ コントローラは、DDR、DDR2、および SDRAM メモリ タイプをサポートします。この互換性により、容量と速度の要件に基づいてメモリを柔軟に選択できます。直接メモリの統合により、プロセッサと外部メモリ デバイス間のデータ転送効率が向上し、継続的なワークロード下でも安定したシステム パフォーマンスがサポートされます。

統合された周辺機器インターフェイス

MPC8548EVUAUJ には、外部デバイスと通信するための DUART、I2C、PCI、および RapidIO インターフェイスが含まれています。これらのインターフェイスは、システムの拡張、ストレージ接続、コンポーネント間の高速データ交換をサポートします。それらの統合により、個別のインターフェイス コントローラーの必要性が減り、組織化されたボード レベルの通信がサポートされます。

783ピンFCBGA表面実装パッケージ

このプロセッサは、約 29 x 29 mm の 783 ボール フリップ チップ ボール グリッド アレイ パッケージに収容されています。この表面実装形式は、コンパクトな基板配置と複数の接続にわたる安定した電気接触をサポートします。パッケージ設計は、ネットワークや組み込み通信機器で使用される高密度レイアウトに適しています。

動作温度範囲 0℃~105℃

指定された動作温度範囲は 0 C ~ 105 C です。この範囲により、制御された産業環境や通信環境で信頼性の高いパフォーマンスが可能になります。長時間の動作中に内部温度が上昇する可能性のあるシステムをサポートします。

IO電圧サポート1.8V、2.5Vおよび3.3V

このデバイスは、1.8 V、2.5 V、および 3.3 V の入力および出力電圧レベルをサポートします。マルチレベル電圧互換性により、幅広い周辺コンポーネントとの接続が可能になります。この柔軟性により、さまざまなロジック規格にわたるシステムの統合が簡素化されます。

MPC8548EVUAUJ 技術仕様

| 製品の属性 | 属性値 |

| メーカー | NXP セミコンダクターズ |

| 電圧 - I/O | 1.8V、2.5V、3.3V |

| サプライヤーデバイスパッケージ | 783-FCBGA (29x29) |

| 速度 | 1.333GHz |

| シリーズ | MPC85xx |

| セキュリティ機能 | 暗号化、乱数生成器 |

| RAMコントローラー | DDR、DDR2、SDRAM |

| パッケージ・ケース | 783-BBGA、FCBGA |

| パッケージ | トレイ |

| 動作温度 | 0℃~105℃(TA) |

| コア数/バス幅 | 1コア、32ビット |

| 取付タイプ | 表面実装 |

| イーサネット | 10/100/1000Mbps (4) |

| コアプロセッサ | PowerPC e500 |

| コプロセッサ/DSP | 信号処理;SPE、セキュリティ。SEC |

| 基本製品番号 | MPC85 |

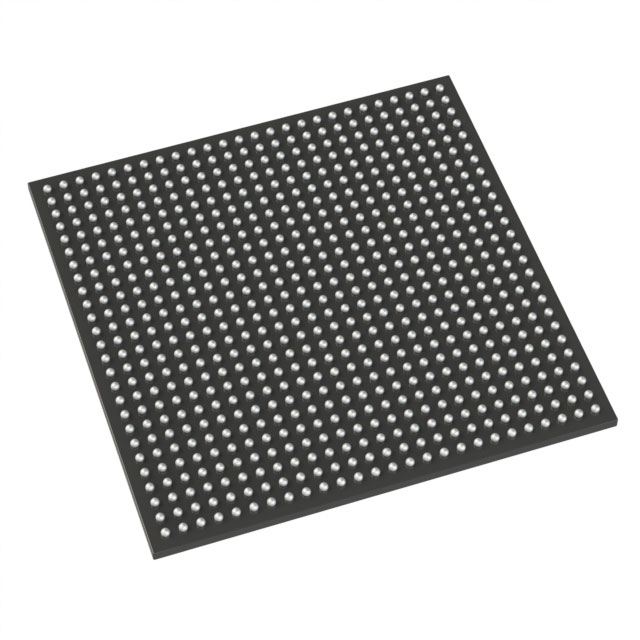

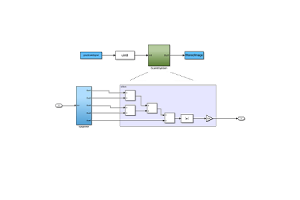

MPC8548EVUAUJのデバイスブロック図

PowerPC e500 コアを中心に統合されたこのアーキテクチャは、32 KB の L1 命令キャッシュと 32 KB の L1 データ キャッシュを、コア複合バスを介して接続された 512 KB の L2 キャッシュと組み合わせます。DDR および DDR2 メモリ コントローラーは外部 SDRAM とインターフェイスし、ローカル バス コントローラーはフラッシュ、SRAM、および GPIO 接続をサポートします。4 つの拡張 3 スピード イーサネット コントローラは、標準 MII および RGMII 関連インターフェイスを通じて 10、100、および 1000 Mbps の動作を提供します。高速接続は、32 ビット PCI および 64 ビット PCI X インターフェイスとともに、Serial RapidIO または PCI Express によって提供されます。暗号化アクセラレーションと乱数生成を備えたセキュリティ エンジンは、XOR エンジンと 4 チャネル DMA コントローラと並行して動作します。サブシステム間の内部データ移動は、Ocean スイッチ ファブリックによって管理され、単一システム オン チップ レイアウト内で処理、メモリ、ネットワーキング、周辺インターフェイスをリンクします。

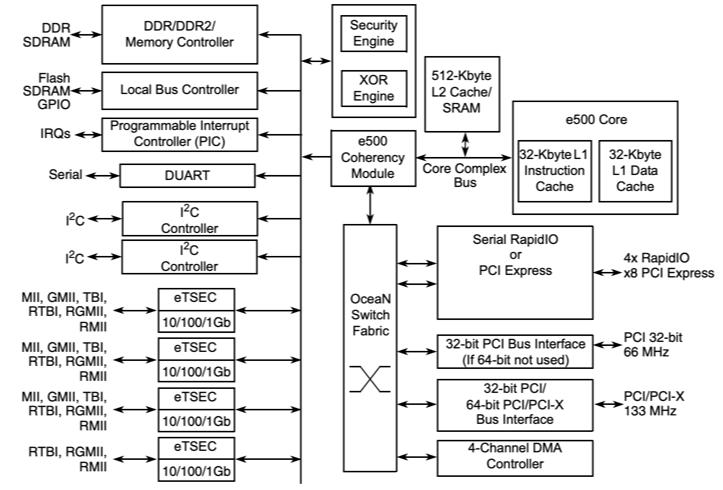

MPC8548EVUAUJのオーバーシュート・アンダーシュート制限

電圧波形制限は、関連する電源レールに対するデバイス インターフェイスでの許容可能なオーバーシュートおよびアンダーシュート レベルを定義します。高レベル入力しきい値は B G L O TVDD を基準とし、破線の境界線で示すように、TVDD プラス 20 パーセントおよび TVDD プラス 5 パーセントまでの一時的なオーバーシュートが許容されます。低レベル制限はグランドを基準とし、マイナス 0.3 V およびマイナス 0.7 V までのアンダーシュート マージンを示します。定常状態範囲を超える過渡変動は、DDR、PCI、I2C、JTAG、イーサネットなどのインターフェイス タイプごとに定義されたクロック基準により、該当するクロック周期の 10 パーセントを超えない期間に制限されます。この図は、信号の完全性とインターフェイスの動作条件への準拠を保証するための電気的ストレス境界を確立します。

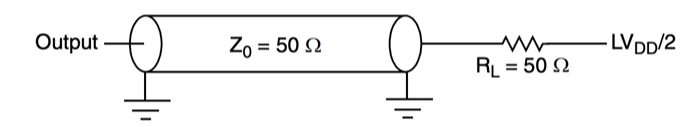

MPC8548EVUAUJのACテスト負荷

出力テスト構成は、eTSEC インターフェイスの AC 特性評価のための制御されたインピーダンス環境を定義します。出力ノードは、50 オームの特性インピーダンスでモデル化された伝送線路を駆動します。この伝送線路は、2 で割った LVDD に接続された 50 オームの負荷抵抗で終端されます。伝送路の両端には接地基準が示されており、平衡測定セットアップを表しています。この構成により、標準化された AC テスト条件下で信号のタイミングと電圧の動作を評価するための、定義された負荷およびバイアス条件が確立されます。

MPC8548EVUAUJの用途

エンタープライズおよびキャリアグレードのネットワークルーター

MPC8548EVUAUJ は、複数のネットワーク ポートにわたる継続的なパケット トラフィックを処理するエンタープライズおよびキャリア グレードのルーターで使用されます。PowerPC e500 コアは、ルーティング テーブル、転送決定、およびプロトコル スタックをリアルタイムで処理します。統合されたクアッド ギガビット イーサネット インターフェイスにより、複数のネットワーク リンクに直接接続できるため、ボード上の外部コンポーネントが減ります。メモリ制御とハードウェア セキュリティ サポートが組み込まれているため、プロセッサは安定したスループットを維持しながら、ローカルおよびワイド エリア ネットワーク全体で暗号化されたデータ ストリームを管理します。

ネットワークスイッチとマルチポートゲートウェイ

マネージド スイッチおよびネットワーク ゲートウェイでは、デバイスは接続されたシステム間のデータ フローを調整します。ポート間の安定した通信を維持しながら、フレーム検査、バッファリング、トラフィック分散を処理します。統合された PCI および RapidIO インターフェイスは、モジュラー システム内の拡張と高速相互接続をサポートします。この設定により、コンパクトなスイッチング プラットフォームで、複数の個別コントローラに依存せずに構造化されたデータ交換を管理できるようになります。

通信インフラ設備

アクセス ユニットや伝送システムなどの通信プラットフォームでは、集中制御とデータ管理に MPC8548EVUAUJ が使用されます。プロセッサは、システム タスクの監視と機能の監視を行いながら、通信インターフェイス間の安定したデータ移動をサポートします。定義された動作温度範囲により、制御されたネットワーク施設で継続的に稼働する機器での使用がサポートされます。

安全なネットワーキングと VPN アプライアンス

セキュア ゲートウェイと VPN アプライアンスは、プロセッサに依存して暗号化されたトラフィックとセッション制御を管理します。統合されたセキュリティ エンジンは暗号化と復号化をチップ上で直接実行し、保護された通信チャネルをサポートします。これにより、追加のセキュリティ プロセッサを必要とせずに安全なリモート接続とデータ交換が可能になり、コンパクトなシステム アーキテクチャの維持に役立ちます。

産業用組み込み制御システム

産業用制御ユニットは、MPC8548EVUAUJ を使用して、ネットワークに接続されたデバイスを監視し、サブシステム間の通信を調整します。構造化された自動化プラットフォーム内でデータ収集、ステータスレポート、および制御信号を管理します。このプロセッサは、長い実行サイクルでも信頼性の高い動作をサポートするため、一日中動作する組み込みシステムに適しています。

高性能組み込みコンピューティング プラットフォーム

組み込みコンピューティング ボードは、このプロセッサを使用して、単一の統合デバイス内でオペレーティング システムと通信サービスを実行します。一貫したパフォーマンスを必要とするシステムのメモリ アクセス、周辺機器制御、およびデータ処理を処理します。統合されたインターフェイスにより、スケーラブルなコンピューティング モジュールをサポートしながらボード設計が簡素化されます。

安全な通信システム

安全な通信機器には MPC8548EVUAUJ が統合されており、有線ネットワーク全体で制御されたデータ交換を管理します。このプロセッサは、保護されたメッセージ処理、安全なキー操作、およびプロトコル監視をサポートします。処理、ネットワーキング、セキュリティ機能を組み合わせることにより、保護されたデータ転送に重点を置いた通信プラットフォームの構造化された設計が可能になります。

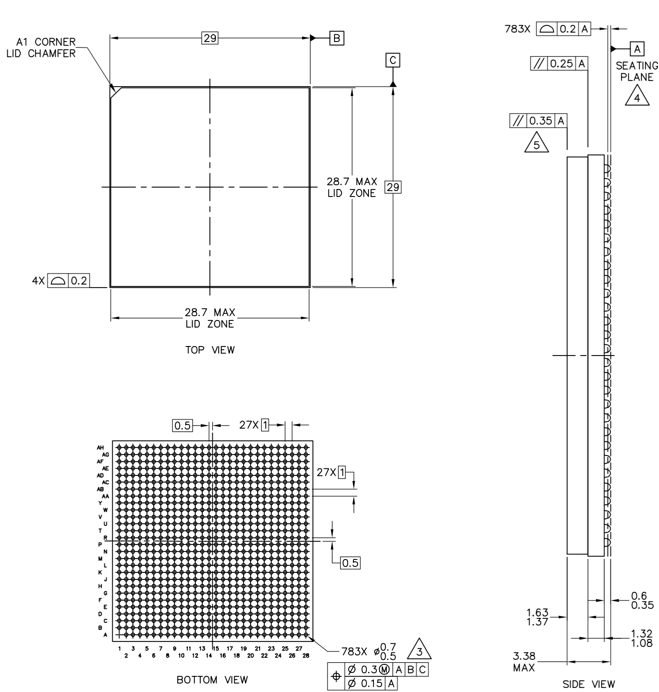

MPC8548EVUAUJの外形寸法

パッケージ外形図は、783 リード FC CBGA およびフルリッド付き FC PBGA バージョンの機械的寸法とボール レイアウトを定義します。上面図では、蓋ゾーンの最大寸法 28.7 x 28.7 mm が指定され、方向付けのための A1 コーナー面取りが特定されます。底面図は、ピンを識別するためにラベル付けされた行と列の座標を含む、0.8 mm ピッチの合計 783 個のはんだボールを含む 27 × 27 のボール グリッド アレイを示しています。側面図には、最大 3.38 mm までの全高制限と座面の基準、および共平面性とプロファイル制御の公差が表示されます。寸法コールアウトと幾何公差により、PCB フットプリント設計とアセンブリの位置合わせの物理的制約が確立されます。

MPC8548EVUAUJのメリットとデメリット

利点

• 最大 1.333 GHz で動作し、ネットワーク システムでの安定したデータ処理をサポートします。

• 4 つのギガビット イーサネット インターフェイスを統合し、外部ネットワーク コントローラの必要性を削減します。

• 安全なデータ処理のためのオンチップ暗号化アクセラレーションと乱数生成機能を搭載

• DDR、DDR2、SDRAM メモリをサポートし、柔軟なメモリ選択が可能

• 構造化されたシステム拡張のためのRapidIOおよびPCIインターフェイスを提供

• 0℃~105℃での動作定格があり、制御された産業環境に適しています。

• 高い統合レベルにより、全体のコンポーネント数が減り、基板レイアウトが簡素化されます。

短所

• シングルコア設計により、並列性の高いソフトウェア環境ではパフォーマンスが制限される可能性があります。

• 統合グラフィックスサポートは含まれていません

• SATA および USB インターフェイスが組み込まれていない

• 783 ピン FCBGA パッケージには正確な PCB レイアウトと制御されたアセンブリが必要です

• PowerPC アーキテクチャは、新しいプロセッサ ファミリと比較して、提供するソフトウェア サポートが狭い可能性があります。

• 長期的なシステム設計を開発する場合は、ライフサイクル計画を見直す必要があります。

MPC8548EVUAUJの代替品

| 部品番号 | メーカー | 主な特長 | 使用例/注意事項 |

| MPC8548EVTAUJD | NXP USA Inc. | PowerPC e500 コア プロセッサは最大 1.33 GHz で動作し、統合 DDR メモリ コントローラと複数のギガビット イーサネット インターフェイスを備えています。高いデータ スループットとネットワーク処理を実現するように設計されています。 | 強力な通信パフォーマンスを必要とするエンタープライズネットワーク機器、通信インフラストラクチャ、および組み込みシステムで使用されます。 |

| MPC8548EVTAUJC557 | フリースケール・セミコンダクター | DDR/DDR2 メモリのサポートと高度な通信インターフェイスを備えた高性能 PowerPC プロセッサ。-40 °C ~ 85 °C の工業用温度範囲をサポートします。 | 拡張温度環境で動作する産業用ネットワーキング、オートメーション コントローラー、通信ゲートウェイに適しています。 |

| MPC8548EVTAUJC | NXP USA Inc. | PowerPC e500 コアには、メモリ コントローラーと高速通信インターフェイスが統合されています。0 °C ~ 70 °C の範囲内で安定した性能を発揮するように設計されています。 | 商用ネットワーキング デバイス、データ ルーティング システム、組み込みコンピューティング プラットフォームで一般的に使用されます。 |

| MPC8548EVUAQG | NXP USA Inc. | 統合されたイーサネットとメモリのサポートを備えた PowerPC ベースのプロセッサで、組み込み通信タスク用に最適化されています。工業用温度機能。 | 産業用ゲートウェイ、ネットワークプロセッサ、高信頼性通信機器に最適です。 |

NXP セミコンダクターズについて

NXP Semiconductors N.V. は、オランダのアイントホーフェンに本社を置く世界的な半導体企業です。企業再編後の 2006 年に設立され、それ以来、ミックスドシグナルおよび組み込み処理ソリューションの主要サプライヤーに成長しました。同社は複数の地域で設計および研究センターを運営し、自動車、産業、通信インフラ、モバイル市場にサービスを提供しています。同社の製品ポートフォリオには、マイクロコントローラー、アプリケーション プロセッサ、安全な識別デバイス、アナログ コンポーネント、接続ソリューションが含まれます。NXP は、輸送、ネットワーキング、組み込みプラットフォームで使用される安全な接続と信頼性の高い電子制御システムに重点を置いています。

結論

MPC8548EVUAUJ は、処理、ネットワーキング、セキュリティを 1 つのコンパクトなチップに統合します。高速で動作する 32 ビット PowerPC コアに加え、4 つのギガビット イーサネット ポートと柔軟なメモリ サポートを備えています。内蔵のセキュリティ エンジンは、暗号化されたデータをプロセッサ上で直接管理するのに役立ち、通信を安定して保護します。PCI、RapidIO、および複数の電圧レベルをサポートしているため、多くの通信および制御システムに適合します。783 ピン FCBGA パッケージにより、要求の厳しいワークロードを処理しながら、高密度のボード レイアウトが可能になります。1 台のデバイスで信頼性の高いデータ ルーティングとシステム制御が必要な場合、このプロセッサはパフォーマンスと統合のバランスの取れた組み合わせを提供します。

データシートPDF

MPC8548EVUAUJ データシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1. MPC8548EVUAUJ は主に何に使用されますか?

MPC8548EVUAUJは主にネットワークと通信で使用されます ルーター、スイッチ、ゲートウェイ、セキュアネットワークなどの機器 家電製品。データルーティング、パケット処理、システムを管理します。 コントロール。イーサネット、メモリ制御、セキュリティが統合されているため 機能を備えているため、継続的に実行して処理を行うシステムでうまく機能します。 安定した交通量。

2. MPC8548EVUAUJ はどのプロセッサ コアを使用していますか?

32 ビット PowerPC e500 コアを使用します。このコアは、 組み込み通信システムと安定した命令処理をサポート そして予測可能なパフォーマンス。最大 1.333 GHz の速度で実行できます。 ネットワーク トラフィックを効率的に処理できるようになります。

3. MPC8548EVUAUJ はハードウェア暗号化をサポートしていますか?

はい、セキュリティ エンジンが組み込まれています。このハードウェアブロックは 暗号化、復号化、および安全なキーの生成を処理します。実行することで これらのタスクはチップ上で直接実行されるため、保護された状態を維持するのに役立ちます 外部セキュリティコンポーネントを追加せずに通信できます。

4. このプロセッサと互換性のあるメモリの種類は何ですか?

プロセッサーは、統合されたプロセッサーにより DDR、DDR2、および SDRAM をサポートします。 メモリコントローラー。これにより、外部を選択する際に柔軟性が得られます。 速度と容量のニーズに基づいてメモリを調整します。メモリの直接統合も可能 プロセッサとメモリ間のスムーズなデータ転送を維持するのに役立ちます デバイス。

5. MPC8548EVUAUJ はどのようなパッケージで提供されますか?

783 ピンのフリップチップ ボール グリッド アレイ (FCBGA) パッケージで提供されます。 大きさは約29mm×29mm。この表面実装フォーマットは、 コンパクトな基板レイアウトで、安定した電気接続を提供します。 ピンが多いため、高密度のネットワーク システム設計に適しています。

シリアル通信プロジェクトに MAX250CSD を選ぶ理由

02/18/2026で公開されています

XC3042-100PC84C PLCC84 パッケージ、ロジック ブロック、および性能

02/18/2026で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/19/8000で公開されています 147783

-

USB-Cピンアウトと機能

04/19/2000で公開されています 112073

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/19/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/19/0400で公開されています 83831

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79646

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 67013

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63136

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63067

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54099

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52229