XC3042-100PC84C PLCC84 パッケージ、ロジック ブロック、および性能

XC3042-100PC84C は、よく知られた XC3000 ファミリの古典的なプログラマブル ロジック デバイスです。これにより、固定機能のチップに依存せずにデジタル ロジックを処理する柔軟な方法が得られます。約 3000 の使用可能なゲートと 5V 動作を備えており、古いボードや長時間稼働するシステムに完全に適合します。電源投入時に構成データをロードすることで再プログラムできるため、アップデートが非常に簡単になります。84 ピン PLCC パッケージは、ボード レイアウトをコンパクトに保ちながら、豊富な I/O 接続を提供します。産業用機械からレトロ コンピューティング プロジェクトまで、このデバイスは信頼性の高いハードウェア設計をサポートし続けます。ここでは、その機能、構造、実際の用途について明確に説明します。カタログ

XC3042-100PC84Cの概要

の XC3042-100PC84C は、構成可能なデジタル ロジック実装用に設計された CMOS SRAM ベースのフィールド プログラマブル ゲート アレイです。これは XC3000 ファミリに属し、84 ピン PLCC パッケージで提供されます。このデバイスは 5 ボルトの電源で動作し、論理機能を定義するために電源投入時に構成データが必要です。その内部構造は、制御、インターフェイス、データ処理タスクのためのプログラマブル ロジック ブロックと柔軟な入出力接続をサポートしています。このコンポーネントは、適応性のあるハードウェア ロジックを必要とする組み込みシステム、産業機器、レガシー デジタル プラットフォームでよく使用されます。XC3042-100PC84C を探しています。現在の在庫、納期、価格を確認するには、お問い合わせください。

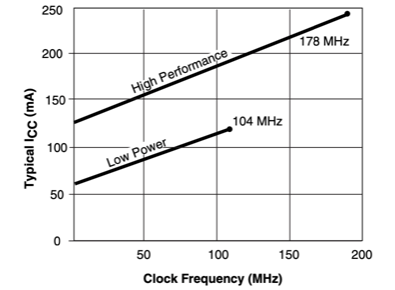

XC3042-100PC84C の標準 Icc 対周波数

グラフは、横軸のクロック周波数(メガヘルツ)に対して、縦軸に代表的な電源電流(ミリアンペア)をプロットしており、動作周波数とともに電流が増加していることを示しています。2 つの動作モードが識別され、「低電力」と「高パフォーマンス」というラベルが付けられ、それぞれが上昇線で表されます。低電力モードは 120 mA 付近の電流で約 104 MHz に達しますが、高性能モードは 240 mA に近い電流で約 178 MHz まで拡張されます。両方の曲線の直線傾向は、スイッチング周波数が増加するにつれて動的電流消費が比例して増加することを示しており、デバイスの周波数依存の電力特性を反映しています。

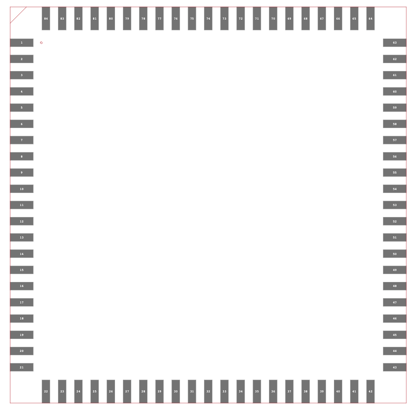

XC3042-100PC84C CADモデル

XC3042-100PC84C 記号

XC3042-100PC84Cのフットプリント

XC3042-100PC84C 3Dモデル

XC3042-100PC84Cの特長

使用可能な論理ゲート容量

XC3042-100PC84C は、デジタル回路の実装に使用可能な約 3000 個の論理ゲートを提供します。この能力は、単一のプログラマブル デバイス内で制御ロジック、データ ルーティング、ステート マシン、および算術演算をサポートします。複数のロジック機能を 1 つのコンポーネントに統合することで、個別の固定ロジック IC の必要性が減り、コンパクトな基板レイアウトがサポートされます。

構成可能なロジックブロック構造

このデバイスには、プログラマブル アーキテクチャの中核を形成する 144 個の構成可能なロジック ブロックが含まれています。各ブロックは、組み合わせ論理関数および逐次論理関数を実行するように配置できます。この構造により、設計者は、予測可能なデジタル操作を維持しながら、アプリケーション要件に基づいてカスタム ハードウェアの動作を定義できます。

ユーザー入力および出力リソース

XC3042-100PC84C には、ユーザーがアクセスできる 74 個の入出力ピンが含まれています。これらのピンにより、外部メモリ、プロセッサ、制御ライン、通信インターフェイスへの直接接続が可能になります。利用可能な IO 数により、組み込みプラットフォームとレガシー プラットフォームでの柔軟なシステム統合がサポートされます。

統合されたオンチップメモリ

このデバイスには、内部構造内に合計 30784 の RAM ビットが組み込まれています。このメモリは、一時的なデータの保存、バッファリング、およびロジック関連の機能に使用できます。RAM が内蔵されているため、適度なストレージのニーズに対して外部メモリへの依存が軽減されます。

標準 5 ボルトの動作範囲

XC3042-100PC84C は、4.75 ボルト~5.25 ボルトの電源電圧範囲内で動作します。この範囲は標準の 5 ボルト デジタル システムと一致しており、確立された設計で一般的に使用される TTL および CMOS ベースの回路との互換性をサポートします。

商用温度範囲

指定された動作温度範囲は 0 ℃ ~ 85 ℃です。これにより、このデバイスは、安定した熱状態が維持される制御された屋内の商業および産業環境に適しています。

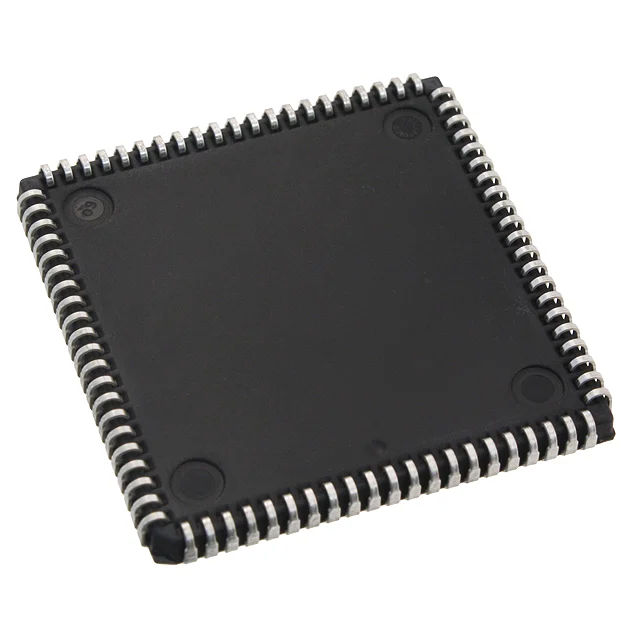

84ピンPLCCパッケージフォーマット

このデバイスは、J リード付きの 84 ピン プラスチック リード付きチップ キャリア パッケージで提供されます。この表面実装形式は、中密度レイアウトでの確実な基板取り付けとプリント基板スペースの効率的な使用をサポートします。

SRAM ベースの再プログラム可能なアーキテクチャ

XC3042-100PC84C は、SRAM ベースの構成システムを使用します。その論理構成は電源投入時に外部ソースからロードされるため、設計の更新が必要なときにデバイスを再プログラムできます。これにより、ハードウェアを交換することなく設計の柔軟性がサポートされます。

XC3000 ファミリ アーキテクチャの互換性

このデバイスは、XC3000 FPGA ファミリのアーキテクチャに従っています。この製品シリーズ内で使用される確立された構成方法と設計アプローチをサポートし、関連デバイスとの一貫した統合を可能にします。

スピードグレード -100 タイミング分類

-100 スピード グレードは、デバイスのタイミング パフォーマンス カテゴリを定義します。これは、XC3000 ファミリ内のスイッチングおよび伝播特性を示し、実際のアプリケーションでの安定した予測可能なデジタル信号の動作をサポートします。

XC3042-100PC84C 技術仕様

| 製品の属性 | 属性値 |

| メーカー | AMDザイリンクス |

| 電圧 - 電源 | 4.75V~5.25V |

| 合計RAMビット数 | 30784 |

| サプライヤーデバイスパッケージ | 84-PLCC (29.31x29.31) |

| シリーズ | XC3000 |

| パッケージ・ケース | 84-LCC (J-リード) |

| パッケージ | トレイ |

| 動作温度 | 0℃~85℃(TJ) |

| LAB/CLB の数 | 144 |

| I/O数 | 74 |

| ゲート数 | 3000 |

| 取付タイプ | 表面実装 |

| 基本製品番号 | XC3042 |

| RoHS ステータス | RoHS非対応 |

| 感湿性レベル (MSL) | 3 (168 時間) |

| リーチステータス | REACHは影響を受けない |

| ECCN | EAR99 |

| HTSUS | 8542.39.0001 |

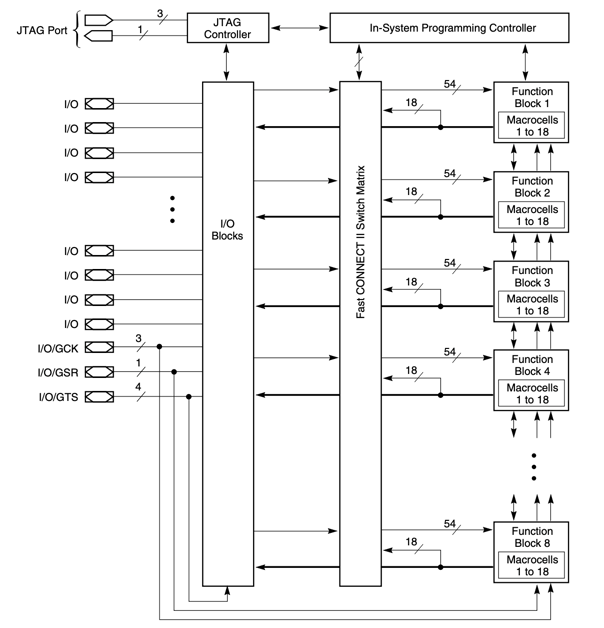

XC3042-100PC84C のアーキテクチャ

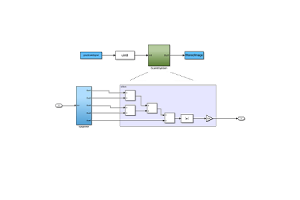

このデバイスは、それぞれ 18 個のマクロセルを含む 8 つの機能ブロックを中心に構成されており、内部信号ルーティングを管理する中央の FastCONNECT II スイッチ マトリックスを介してプログラマブル ロジック リソースを接続します。各機能ブロックは、54 の入力ラインと 18 の出力パスを使用してマトリックスとインターフェイスし、CPLD 構造に特有の予測可能な相互接続遅延をサポートします。左側に沿って配置された I/O ブロックは外部ピン接続を提供し、クロック、セット リセット、およびトライステート分配用の I O GCK、I O GSR、および I O GTS というラベルが付いたグローバル制御信号を統合します。JTAG コントローラーとシステム プログラミング コントローラーが上部に表示され、バウンダリ スキャン準拠と再プログラム可能な構成機能を示します。太字の信号パスは、機能ブロックの出力から IO ブロックへの直接接続を示しており、選択した出力の配線ステージが削減されます。

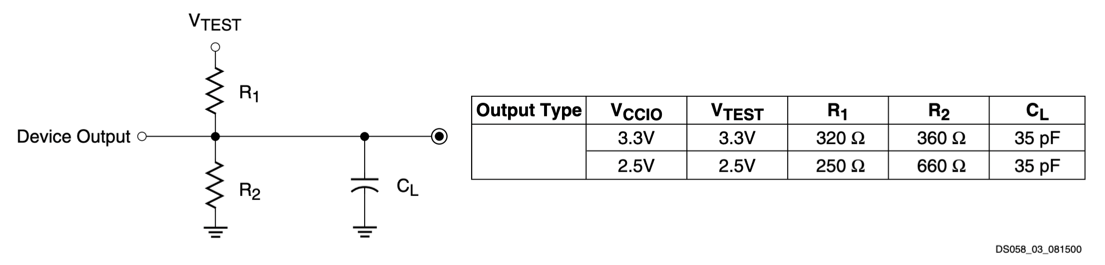

XC95144XLのAC負荷回路

テスト負荷構成では、デバイスの出力を、VTEST に接続された R1 とグランドに接続された R2 によって形成される抵抗分圧器に接続し、出力ノードからグランドに容量性負荷 CL が接続されます。この回路は、制御された抵抗負荷と容量負荷を定義することにより、AC タイミング測定の出力スイッチング条件をモデル化します。表には、2 つの動作レベルの値が指定されています。VCCIO と VTEST は、320 オームの R1 と 360 オームの R2 を使用して 3.3 V に設定され、または 250 オームの R1 と R2 を使用して 2.5 V に設定されますが、どちらの場合も CL は 35 pF のままです。この構成は、定義された電圧条件下で出力の立ち上がりおよび立ち下がり特性を評価するための標準化された負荷パラメータを確立します。

XC3042-100PC84Cの用途

レガシー組み込みシステムのメンテナンス

XC3042-100PC84C は、プログラマブル ロジックの初期採用中に開発された組み込みシステムを保守するために広く使用されています。製造装置、計装、通信ハードウェアの多くの制御ボードは、XC3000 アーキテクチャを中心に設計されています。これらのシステムの修理が必要な場合、このデバイスを使用すると、プリント回路基板を変更せずに元のプログラマブル ロジックを復元できます。これは、システムの動作、タイミング関係、信号の互換性を維持するのに役立ちます。

XC3000 アーキテクチャに基づく産業用制御システム

XC3000 シリーズ デバイスで構築された産業用制御プラットフォームでは、XC3042-100PC84C がシーケンス、信号ルーティング、センサーとアクチュエーター間のインターフェイス調整を管理します。5 ボルトの動作範囲は、古いオートメーション システムで使用されているロジック レベルと一致します。このデバイスは、プログラマブル ハードウェア内でタイミング制御、データ パス管理、ディスクリート ロジックの置き換えを処理できるため、長期稼働の実稼働環境でも安定した動作が可能になります。

レトロ コンピューティングとハードウェア修復プロジェクト

XC3042-100PC84C は、初期のプログラマブル ロジック設計を保存または再作成することを目的としたレトロ コンピューティング プロジェクトで使用されます。これにより、元々 XC3042 デバイスで構築された拡張カード、開発ボード、インターフェイス モジュールの復元が可能になります。同じ構成構造とピン レイアウトをサポートすることで、設計ファイルが利用可能な場合に再プログラミングを可能にしながら、本物のハードウェア動作を維持するのに役立ちます。

初期のFPGAアーキテクチャの教育的研究

このデバイスは、第一世代の SRAM ベースの FPGA 構造を理解するための教育プラットフォームとして機能します。学生は、実際のハードウェア デバイスで構成可能なロジック ブロック、内部メモリ リソース、および外部構成方法を調べることができます。このアーキテクチャを使用すると、初期のプログラマブル ロジック システムがどのように編成され、デジタル機能がハードウェアにどのようにマッピングされたかについての実用的な洞察が得られます。

既存の XC3042 設置環境での直接交換

XC3042-100PC84C は、すでに XC3042 シリーズ コンポーネントを使用しているシステムのドロップイン交換品として機能します。同じパッケージ形式、電圧範囲、アーキテクチャ構造をサポートしているため、老朽化した機器の修理や改修が可能です。このアプローチにより、再設計や新しいプログラム可能なプラットフォームへの変換を必要とせずに、レガシー システムの耐用年数が延長されます。

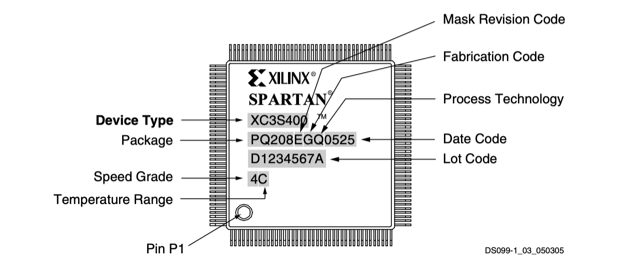

デバイス部品のマーキング XC3042-100PC84C

パッケージの図は、注文情報を定義するラベル付き部品マーキング フィールドを備えた TQ144 デバイスの上面図を示しています。デバイス タイプは、ファミリー指定を示す XC95xxxXL として表示され、パッケージ コード TQ144 は 144 ピン薄型クアッド フラット パッケージを識別します。スピード グレードは 7C とマークされており、数値はタイミング性能を示し、文字は商用動作温度範囲を示します。デバイスの部品番号に関連しない別の水平線が示され、トレーサビリティまたはロット情報と注文識別子が区別されます。ピン 1 の位置は、パッケージの方向を定義するために 1 つの角に円形のインジケーターでマークされています。

XC3042-100PC84C の長所と短所

利点

• SRAMベースの構造により、設計変更が必要な場合にロジックを再プログラムできます。

• 確立された XC3000 アーキテクチャにより、レガシー システムの長期にわたる安定した運用をサポート

• 5 ボルトの電源範囲は古い TTL および CMOS ロジック レベルに一致します

• 適度なゲート数は小規模から中規模のデジタル制御タスクに適合します。

• 一般的に、初期の組み込みおよび産業用プラットフォームに統合されています

• 84ピンPLCCパッケージはコンパクトな表面実装ボードレイアウトをサポート

短所

• 5 ボルト動作は最新の低電圧デジタル システムに適合しません。

• 現世代の FPGA デバイスと比較してロジック容量が制限されている

• 消費電力は、新しい低電圧プログラマブル ロジック ファミリよりも高い

• 内蔵乗算器と専用の信号処理リソースが不足している

• 高度なクロック管理機能や高速インターフェイス機能は含まれていません。

• 最新の FPGA 設計環境では開発ツールの互換性が制限されています

XC3042-100PC84Cの代替品

| 部品番号 | メーカー | 主な特長 | 使用例/注意事項 |

| XC3042-100PQ100C | AMD | 約 3,000 個のシステム ゲートと 144 個の構成可能なロジック ブロックを備えた XC3000 ファミリ FPGA。5V電源で動作し、表面実装パッケージをサポートします。 | 従来のプログラマブル ロジック設計、インターフェイス制御、および中程度の密度のデジタル アプリケーションで使用されます。 |

| XC3042-125PQ100C | AMD | 代替スピード グレードを備えた同様の XC3042 デバイス。PQFP パッケージで構成可能なロジック リソースと柔軟な I/O を提供します。 | タイミング要件が緩やかなデジタル制御および通信回路に適しています。 |

| XC3030L-8VQ64C | AMD | 構成可能なロジック ブロックとコンパクトなパッケージ設計を備えた XC3000L シリーズの低消費電力 FPGA。消費電力を削減するように設計されています。 | 電力に敏感な組み込みシステムや家電製品に適しています。 |

| XC3030L-8VQ64I | AMD | 拡張された温度範囲と柔軟なプログラマブル ロジック リソースを備えた工業用グレードの低消費電力 FPGA。 | より過酷な環境で信頼性の高い動作を必要とする産業用制御システムや組み込みシステムで使用されます。 |

AMDザイリンクスについて

AMD ザイリンクスは、Advanced Micro Devices, Inc. のアダプティブおよびエンベデッド コンピューティング部門として運営されています。この組織の起源は、1984 年にカリフォルニアで設立された Xilinx, Inc. であり、製造後に構成できるプログラマブル ロジック デバイスを導入しました。同社は長年にわたり、通信インフラストラクチャ、産業オートメーション、航空宇宙システム、自動車エレクトロニクス、およびデータセンターの高速化で使用されるプログラマブル プラットフォームに拡大してきました。そのポートフォリオには、プログラマブル ロジック デバイス、適応型システム オン チップ プラットフォーム、開発ソフトウェア、ハードウェア レベルのカスタマイズをサポートする設計ツールが含まれます。2022 年の AMD による買収後、そのテクノロジーはプログラマブル ロジックと高性能処理ソリューションを組み合わせた、より広範な半導体ポートフォリオの一部になりました。

結論

XC3042-100PC84C は、5V デジタル システムでプログラマブル ロジックを管理するための実用的な方法を提供します。SRAM ベースの構造により、必要に応じていつでも設定をリロードおよび更新できます。ロジック容量、内部 RAM、および柔軟な I/O 接続の確実な組み合わせを提供します。PLCC84 パッケージにより、多くのボード レイアウトに簡単に統合できます。古い機器を保守している場合でも、修復プロジェクトに取り組んでいる場合でも、このデバイスは元のハードウェアをスムーズに実行し続けるのに役立ちます。互換性と柔軟性が重要な場合には、引き続き信頼できる選択肢となります。

データシートPDF

XC3042-100PC84C データシート:

関連情報

ALLELCO LIMITED

もっと見る

クイックお問い合わせ

お問い合わせを送ってください、すぐに返信します。

一般的な問題 [FAQ]

1. XC3042-100PC84C はどのようなタイプのデバイスですか?

XC3042-100PC84C は、CMOS SRAM ベースのフィールド プログラマブル ゲートです。 アレイ(FPGA)。XC3000 ファミリに属しており、以下を定義できます。 電源投入時に構成データをロードすることにより、カスタム デジタル ロジックを実行できます。これ つまり、ハードウェアを交換せずに動作方法を変更できるということです。

2. XC3042-100PC84C にはどのような電源電圧が必要ですか?

標準の5Vに一致する4.75V~5.25Vの範囲内で動作します。 デジタルシステム。これにより、多くの古い TTL および CMOS との互換性が得られます。 従来のボードによく見られる回路。

3. XC3042-100PC84C はいくつのロジック リソースを提供しますか?

このデバイスは約 3000 の使用可能な論理ゲートを提供し、144 の論理ゲートが含まれます。 構成可能な論理ブロック。ユーザーがアクセスできる 74 個の I/O ピンも備えています 一時的なデータストレージ用の 30,000 ビットを超える内部 RAM 論理関数。

4. XC3042-100PC84C はインストール後に再プログラムできますか?

はい、できます。SRAMベースの構成を使用しているため、新しいものをロードできます。 システムの電源を入れるたびに構成データが保存されます。これによりアップデートが可能になります チップを物理的に交換することなく設計を変更できます。

5. XC3042-100PC84C はどこで一般的に使用されますか?

組み込みシステムや産業用制御でよく見られます。 機器やレトロ コンピューティング プロジェクトなど。特に便利なのは、 XC3000 アーキテクチャを中心に構築されたハードウェアの保守または復元。

MPC8548EVUAUJ のブロック図とパフォーマンス機能について

02/18/2026で公開されています

4.7 kΩ 抵抗ガイド: カラー コード、用途、テスト、値の比較

02/16/2026で公開されています

ホットポスト

-

複雑な命令セットコンピューター:コンピューティングをどのように変更しましたか?

04/19/8000で公開されています 147781

-

USB-Cピンアウトと機能

04/19/2000で公開されています 112062

-

Xilinx Unified Simulation Primitivesの使用:FPGAの設計とシミュレーションの包括的なガイド

04/19/1600で公開されています 111352

-

電子機器における電源電圧: VCC、VDD、VEE、VSS、および GND の意味

04/19/0400で公開されています 83816

-

RJ45コネクタガイド:ピンアウト、配線、ケーブルタイプ、および使用

01/1/1970で公開されています 79630

-

現代の電気システムにおけるワイヤカラーコードの究極のガイド

電気システムの使用方法は、色だけではありません。各ワイヤーの色は特定の機能を示し、設置とメンテナンス中に電気コンポーネントを正しく識別して処理しやすくなります。これは、運用プロセスをスピードアップするだけでなく、間違いの可能性を減らし、ユーザーと技術者の両方を安全に保つのに役立ちます。この記事では、ワイヤーカラーコードの重要性、安全性と機能への影響、およびそれらを導くグローバル基準について説...01/1/1970で公開されています 66998

-

パージバルブガイド:機能、症状、テスト、および最適なエンジン性能の交換

パージバルブは、大気に逃げる前に燃料蒸気を管理することで空気を清潔に保つのに役立つ車のシステムの重要な部分です。これは、汚染を減らすことで環境を支援するだけでなく、車の走行を改善し、燃料をより効率的に使用するようにします。この記事では、パージバルブの作業方法、タイプ、適切に機能しているかどうかを確認する方法など、パージバルブの詳細について説明します。 <h2 style=...01/1/1970で公開されています 63124

-

品質(Q)係数:方程式とアプリケーション

質の高い要因、または「Q」は、無線周波数(RF)を使用する電子システムでインダクタと共振器がどれだけうまく機能するかをチェックするときに重要です。「Q」は、回路がエネルギーの損失を最小限に抑え、システムが主要な周波数を中心に処理できる周波数の範囲にどの程度適切に影響するかを測定します。インダクタ、コンデンサ、および調整された回路を備えたシステムでは、より高い「Q」は、回路が特定の周波数に焦点...01/1/1970で公開されています 63057

-

最大電力伝達定理でピーク性能を達成します

最大電力伝達定理は、バッテリーや発電機などのソースからのエネルギーが接続荷重にどのように流れるかを説明します。これは、負荷が最もパワーを受ける正確な条件を示しています。この記事では、定理の意味、DC回路とAC回路の両方でどのように機能するか、その背後にある証拠、その実生活のアプリケーション、およびその利点と短所について説明します。最後に、この原則がソーラーパネル、ラジオ、スピーカー、さらには...01/1/1970で公開されています 54097

-

A23バッテリー仕様と互換性

A23バッテリーは、高電圧の小さなシリンダー型のバッテリーです。23A、23AE、またはMN21とも呼ばれ、12ボルトで走行し、AAまたはAAAバッテリーよりもはるかに高くなっています。その特別なデザインにより、小さいながらも強力な電源が必要なガジェットに最適です。この記事では、A23バッテリーの機能、パフォーマンス、および使用について説明します。さまざまなブランドやその他...01/1/1970で公開されています 52208